El set de instrucciones ARM, es sin duda la ISA más utilizada en una CPU en el mundo. Decenas de miles de millones de dispositivos así lo corroboran y el hecho de que se utilice en diferentes mercados, desde simples microcontroladores hasta como la CPU central de complejos centros de datos, pasado por teléfonos móviles, consolas de videojuegos y televisores inteligente. En este artículo os repasamos la arquitectura base de esos microprocesadores así como sus primeros años de historia.

Historia de los microprocesadores ARM

Si bien la actual ARM Holdings, la empresa, fue fundada en 1990, la existencia de estas CPU se remonta a 1983, fecha en la que la encargada de hacerlos fue Acorn Computers, quien por mandato de la cadena televisiva BBC creó un coprocesador para el llamado BBC Micro, un microordenador británico basado en el MOS 6502. No obstante, sus ingenieros, temiendo que el sistema se volviera anticuado, decidieron crear la posibilidad de montar una CPU más potente.

En principio iban a usar uno de un fabricante tercero, pero decidieron crear su propio microprocesador, ya que se sentían frustrados de las alternativas que había en el mercado. Consideraban que las CPU existentes en el mercado en ese momento (68000 e Intel 80286) tenían un mal sistema de gestión de memoria, eran lentos a la hora de procesar sus instrucciones en comparación con el 6502 si se comparaban a igualdad de ciclo de reloj. ¿El problema de la CPU de MOS? No podían crear código para esta en un lenguaje de programación de alto nivel (C, BASIC…) por lo que al final decidieron crear su propia CPU y es así como nació el ARM 1.

La idea inicial para el primer chip fue crear un clon del 65816 de Western Digital, pero aplicando la misma filosofía que el RISC I de la universidad de Berkeley, pero este nunca salió del laboratorio, dado que nunca se vendió comercialmente.

La finalización del primer chip

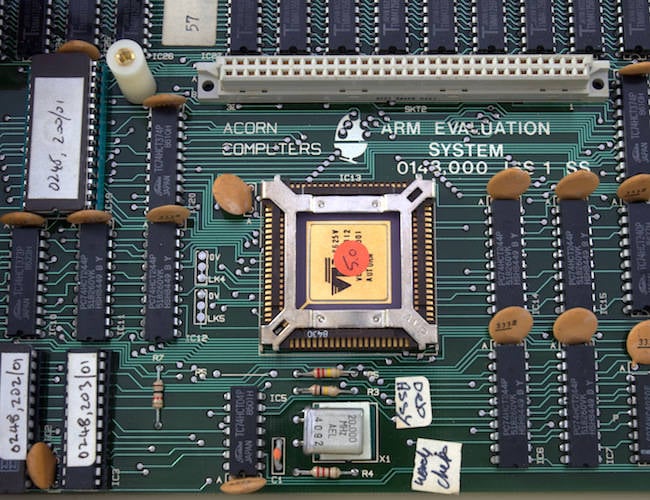

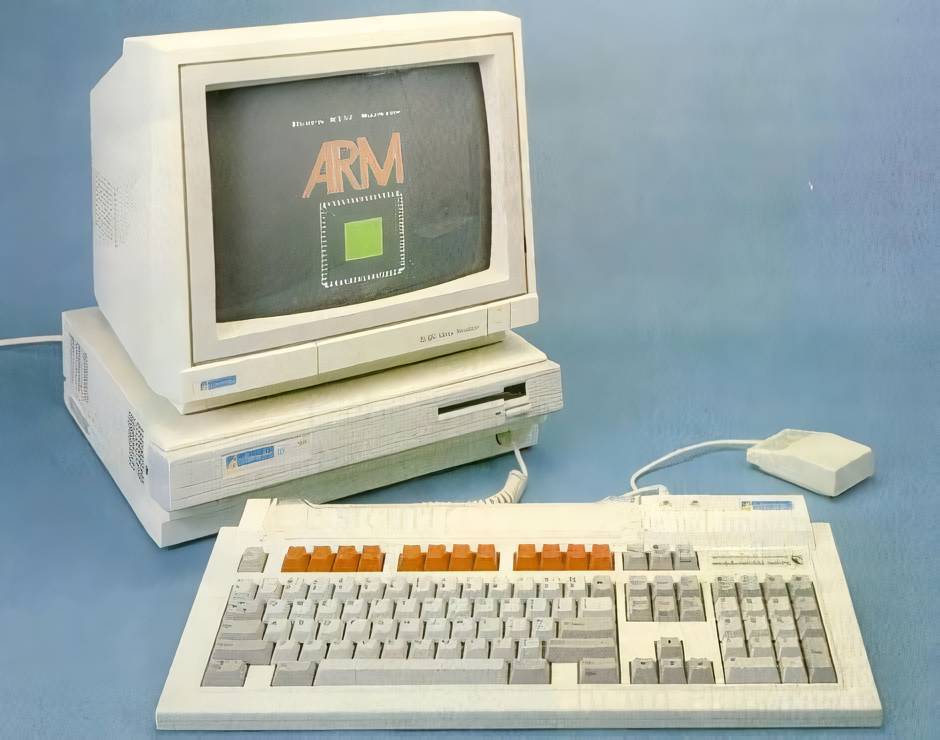

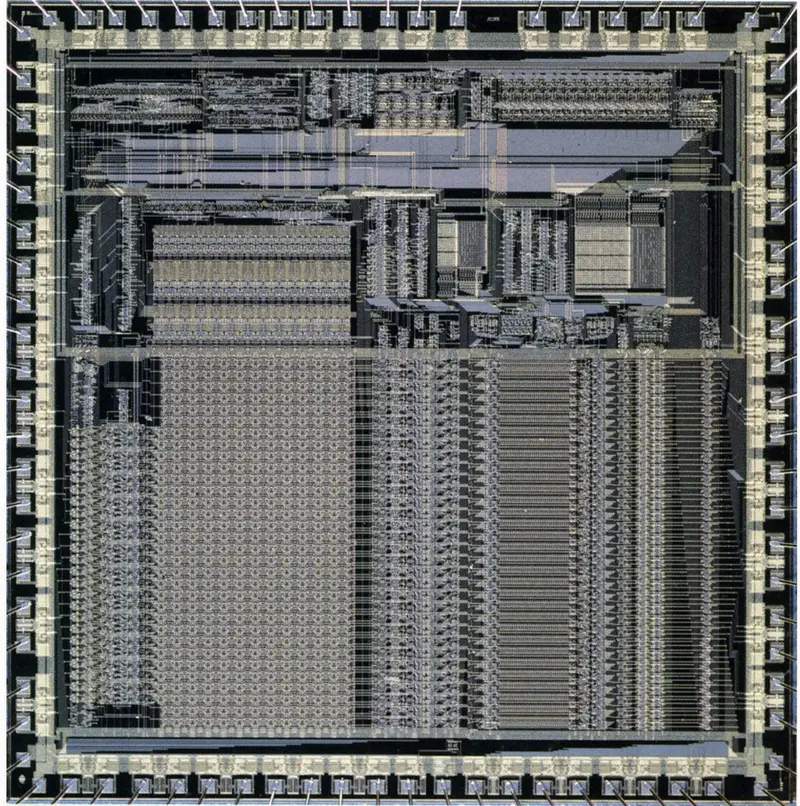

Ya en el 1985 y tras 18 meses de trabajo, tenían el primer chip. Se trataba de una pieza de 25.000 transistores, por lo que a simple vista era menos compleja que otras CPU del momento. El 386 de Intel, que fue terminado oficialmente ese año, disponía de 275.000 transistores, unas diez veces más. Pero hemos de tener en cuenta que el ARM 1 buscaba competir frente al 68000 de Motorola y los 29000 transistores del 8086 de Intel, pero con una capacidad muy superior a este último en lo que a potencia de cálculo se refiere.

No solo eso, sino que el chip se diseñó para funcionar a potencias muy bajas, lo que certificó el futuro de la arquitectura para sistemas que iban a pilas o usando batería recargable. ¿El motivo detrás de ello? No querían usar recubrimiento cerámico, ya que este era muy caro, y prefirieron apostar por el plástico para recubrir el chip. Es por ello que diseñaron su CPU para funcionar a 1 W. El fabricante del chip fue VLSI Design, quienes lo manufacturaron bajo un proceso de 3 micrómetros, y sí, hablamos en teoría de transistores 1000 veces más grandes que los actuales.

Eso sí, este primer chip no se llegó a comercializar jamás, pero sí que sirvió como base para el ARM 2, el cual fue el primer chip comercial que salió al mercado con dicho set de instrucciones y mostrar sus características únicas al mundo, apenas tenía 5.000 transistores más respecto al primer modelo, pero Acorn Computers tenía planes más ambiciosos que el hacer un simple coprocesador para un ordenador de juguete.

Barriendo el suelo con el 68000

Pese a conseguir completar su chip, no estaban del todo contentos con el rendimiento del primer chip, por lo que decidieron rehacerlo internamente para reducir el tiempo de cada una de las instrucciones en lo máximo posible, mientras mantenían la compatibilidad hacia atrás con el diseño original conservando una serie de elementos que terminarían siendo comunes en posteriores generaciones. Hablamos de características como un bus de datos de 32 bits, uno de direccionamiento de 26 bits (el límite eran 64 MB de memoria), 16 registros de propósito general, pero por encima de todo el hecho de adoptar una filosofía RISC en el diseño.

Mientras que un 68000 requería funcionar a 8 MHz para alcanzar 1 MIPS de potencia, el ARM 2 lo hacía con solo 2.63 MHz de velocidad y los primeros modelos del chip funcionaban a 6 MHz. Es decir, habían conseguido crear una CPU con solo 30.000 transistores que duplicaba en rendimiento al 68000 de Motorola y que para colmo solo consumía 1 W. Pensad que hablamos de la época de las primeras generaciones del Commodore Amiga y del Atari ST.

El Acorn Archimedes

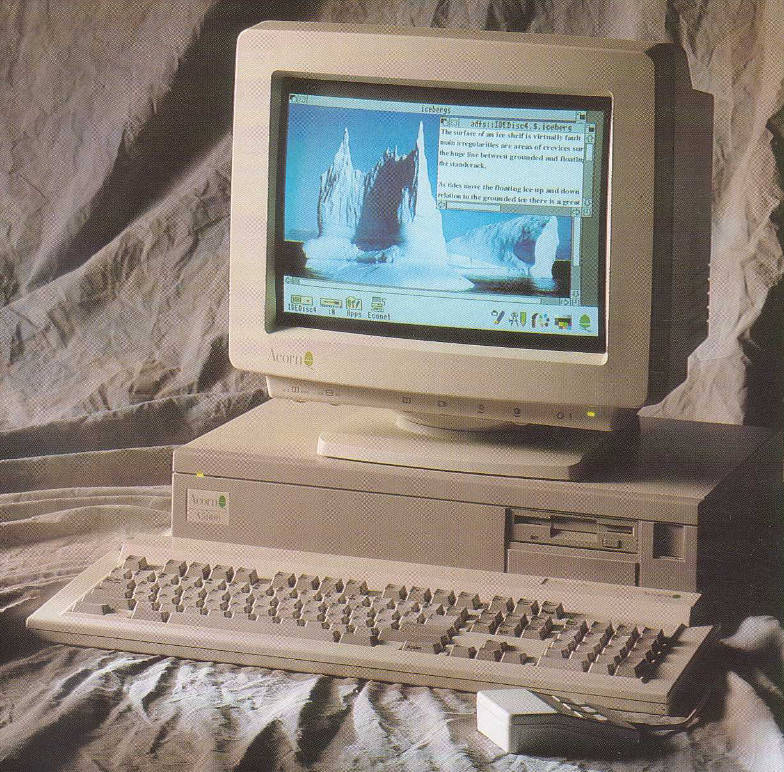

En 1987 Acorn Computers decidió lanzar su propio ordenador basado en la arquitectura que habían creado, al cual bautizaron como Archimedes, el cual lanzaron a mediados de 1987 al mercado con 3 chips de apoyo: uno para el acceso a memoria, otro para controlador de vídeo y un tercero para controlar los periféricos, además de soportar una FPU ex. Debido a que era un set de instrucciones inédito en la industria, tuvieron que crear su propio sistema operativo, sus herramientas para compilar. Obviamente, era imposible competir con otras plataformas ya asentadas y la falta de software para dicho sistema lo acabó condenando.

Sí, con el ARM 1 la gente de Acorn Computers había aprendido a diseñar un microprocesador propio, con ARM 2 fueron más allá y terminaron por diseñar un sistema al completo, incluyendo los chips periféricos que se necesitaban para crear un ordenador. Además, incluyeron un modo supervisor para que el sistema operativo se ejecutara en un espacio en el direccionamiento de memoria protegido. No obstante, hemo de aclarar que, pese a seguir la ideología de diseño RISC, ARM no jugaba todavía en las grandes ligas del rendimiento, ya que si bien obtenia mejor rendimiento que un Amiga o un Atari ST,

ARM3

La segunda generación de la arquitectura ARM nació con el tercero de sus chips, el ARM 3, el cual se usó como CPU principal de Acorn Archimedes A5000, un ordenador que se lanzó en 1991 con una serie de mejoras respecto al modelo de 1987 que fueron más allá del soporte para el nuevo procesador. Entre otras cosas se incluyó un controlador de vídeo VGA, los mismos puertos de serie y en paralelo que los utilizados en PC y soporte para disquetes de 3.5 pulgadas de doble cara y doble densidad. Así como un puerto IDE para poder conectar un disco duro interno.

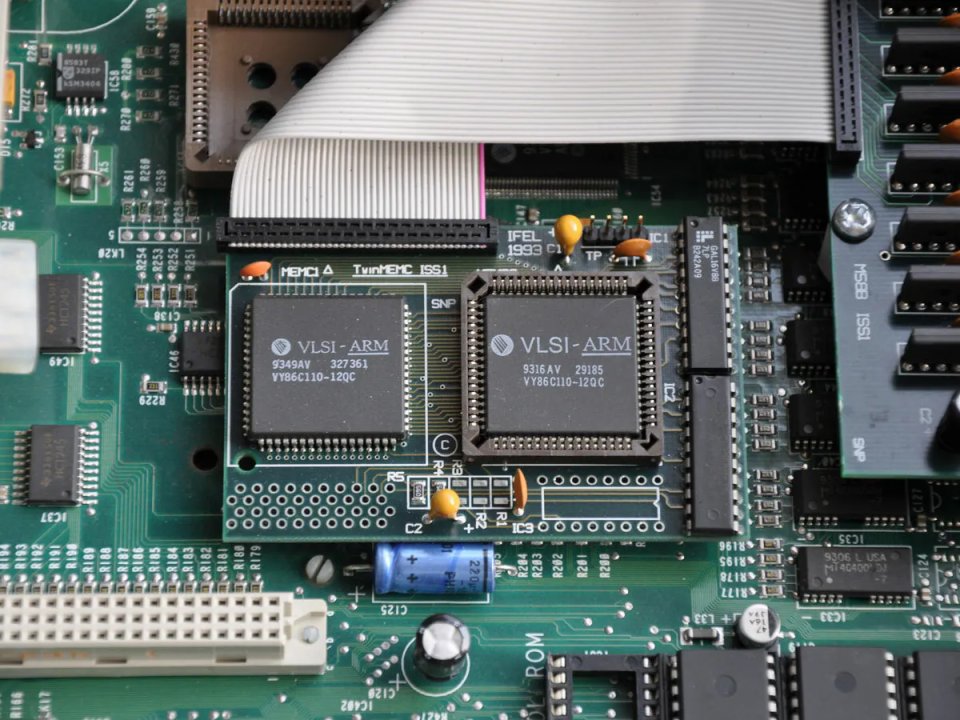

La realidad es que comercialmente los ordenadores Archimedes eran un fiasco comercial, pero en Acorn Computers no se rindieron, ya que operativamente habían separado su división de ordenadores de la de diseño de microprocesadores, permitiendo a esta última vender sus soluciones a terceros. Siendo el ARM3 la primera CPU que ofertaron a universidades y centros de investigación. En cuanto a las mejoras del ARM3, está el hecho que consiguieron que la CPU pudiese trabajar a una velocidad de 25 MHz y el añadido de una memoria caché de primer nivel con 4 KB compartidos entre datos e instrucciones.

Su rendimiento por ciclo de reloj era de 0.55 MIPS gracias al añadido de la caché, pero al coste de un aumento considerable del número de transistores para el sistema, el cual pasaron a ser 310.000. Un salto diez veces mayor que en la anterior generación, pero inferior a las bestias de 1 millón de transistores como el 486 de Intel o el Motorola 68040 que fueron lanzados más o menos por la misma época.

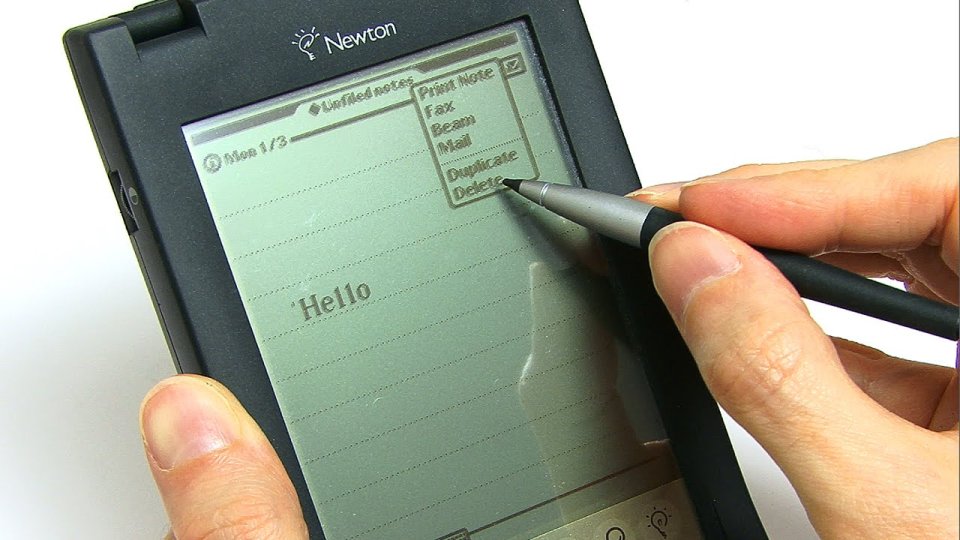

La entrada de Apple con el Newton MessagePad

Por aquel entonces Apple se encontraba diseñando lo que terminaría siendo el primer asistente personal u ordenador de bolsillo, el Newton Message Pad. En Cupertino se dieron cuenta de una dolorosa verdad, las CPU de la familia 68000 de Motorola pese a que les iban a facilitar portar el código desde la plataforma Macintosh al nuevo sistema, eran demasiado calientes y consumían demasiado como para colocarse en un dispositivo de bolsillo, por lo que terminaron fijándose en el ARM 3 como microprocesador alternativo, especialmente por las características de la arquitectura a la hora de trabajar con temperaturas y consumos bajos.

Esto se traducía en un suculento contrato para Acorn Computers, pero la condición de la mano de Apple es que la división de microprocesadores se convirtiera en un ente separado. De esta manera nació ARM Holdings, cuyo modelo de negocio sería el diseño de chips a terceros y la fabricación, siendo el cliente con privilegios Apple. Ya bajo la nueva empresa diseñaron la arquitectura ARM6, la cual amplió el bus de direcciones a 32 bits y se fabricó a 0.8 micrómetros, y se le añadió un búfer de escritura, lo que aumentó el rendimiento por ciclo un 40% adicional, respecto al ARM 3.

En realidad, no era más que un ARM 3 adaptado a las necesidades de Apple, siendo el cambio más importante la inclusión de una unidad MMU paginada en el diseño, lo cual le permitió correr sistemas operativos como UNIX, haciéndolo viable como un microprocesador para competir en las grandes ligas de las CPU RISC, pero su mayor victoria fue poder tener un mercado exclusivo, el de los dispositivos de bajo consumo, el cual sería la clave de su supervivencia en el futuro y donde se consolidaría hasta el dia de hoy.

Arquitectura general de los microprocesadores ARM

A continuación os haremos una descripción general de las características comunes de todas las CPU ARM de 32 bits, ya que al contrario de lo que ocurrió con los x86 donde el salto a los 64 bits fue una extensión de lo ya existente, en el caso de ARM fue un cambio bastante profundo que provoca ciertas incompatibilidades. No es el único caso, ya que tenemos elementos como la unidad de predicción de saltos avanzadas en los ARM10 en adelante, las instrucciones Thumb en los ARM7 en adelante, o las diferentes extensiones SIMD que ha tenido la arquitectura durante toda su historia.

En esta sección hemos decidido centrarnos en lo básico, en lo que tienen todas la CPU ARM en común, más que nada por el hecho que introduciremos las diferentes mejoras a la hora de hablar de sistemas en concreto. Por ejemplo, tenemos planeado hablar de las particularidades del ARM7 en la futura entrada sobre Game Boy Advance. Así pues, lo que tenéis a continuación son los elementos comunes de la arquitectura, presentes desde el nunca lanzado ARM1 hasta hoy en día, pero en el modo de 32 bits, si que este se sigue implementando a día de hoy y no ha sido borrado definitivamente del mapa.

Acceso a la memoria

Lo que llevó a Sophie Wilson a sentirse frustrada con los diseños de CPU existentes en los años 80 fue la ineficiencia en el acceso secuencial a memoria. En la mayoría de microprocesadores de la época, incluso al leer datos contiguos, se debía reiniciar la comunicación con la memoria RAM en cada acceso, lo que implicaba perder valiosos ciclos de reloj en tareas repetitivas. Esta limitación inspiró al equipo de Acorn a diseñar una arquitectura completamente nueva: ARM, con un enfoque centrado en la eficiencia.

Para resolver este problema desde el diseño inicial del chip ARM, implementaron dos innovaciones clave.

- Pines SEQ y ABORT: se añadieron dos señales nuevas al bus de control. El pin SEQ (sequential) permitía mantener abierta la comunicación con la memoria durante accesos consecutivos. Así, al leer direcciones contiguas, el sistema evitaba reabrir la fila de memoria, incrementando simplemente la dirección de columna. Esto reducía la latencia significativamente. El pin ABORT, por su parte, ofrecía un mecanismo seguro para cancelar accesos a memoria en caso de errores o interrupciones, algo que mejoraba la fiabilidad sin penalizar el rendimiento.

- Delegación al controlador de memoria externo: en lugar de que el microprocesador controlase directamente el acceso a la RAM, esta responsabilidad se delegó a un controlador externo. ¿El beneficio? Mientras otras arquitecturas introducían ciclos de espera si la memoria era lenta, ARM permitía ajustar dinámicamente la velocidad de acceso, adaptándose al tiempo de respuesta de la RAM. Esto eliminaba esperas innecesarias y mantenía la CPU activa el mayor tiempo posible.

Todo ello reducía la cantidad de ciclos muertos del microprocesador, especialmente en los accesos a memoria secuenciales, que son los más comunes a la hora de ejecutar un programa.

La R de ARM significa RISC

Las CPU con ISA ARM, al igual que el resto de microprocesadores que usan un set de instrucciones y registros concreto dispone de una configuración común para todos los habitantes de la familia a partir de la cual derivan el resto de familias y generaciones. En principio se trata una arquitectura del tipo RISC, cuya filosofía general era la de poder conseguir que la mayoría de instrucciones se ejecuten en un solo ciclo de reloj, siguiendo la siguiente normativa:

- Instrucciones: Conjunto reducido / Ciclo único / Longitud fija

- Conjunto reducido: Utiliza un número limitado de instrucciones simples para facilitar la implementación y acelerar la ejecución.

- Ciclo único: Cada instrucción se ejecuta en un solo ciclo de reloj, lo que mejora el rendimiento predecible.

- Longitud fija: Todas las instrucciones tienen el mismo tamaño (por ejemplo, 32 bits), lo que simplifica la decodificación.

- Pipeline: Decodificación en una sola etapa / Sin necesidad de microcódigo

- Decodificación en una sola etapa: Permite una interpretación rápida de la instrucción durante el pipeline.

- Sin microcódigo: La lógica está directamente implementada en hardware, sin necesidad de microprogramas como en arquitecturas CISC.

- Registros: Conjunto amplio de registros de propósito general

- Registros de propósito general: Ofrece muchos registros accesibles para almacenar datos temporalmente durante las operaciones.

- Ventaja: Menor dependencia de memoria, lo cual mejora el rendimiento.

- Arquitectura de carga/almacenamiento (Load/Store)

- Separación de instrucciones: Las instrucciones de procesamiento de datos operan solo sobre registros, mientras que las de carga/almacenamiento acceden a la memoria.

- Ventaja: Mejora la eficiencia del pipeline y reduce dependencias con la memoria.

Sin embargo, ARM se diferencia del resto de microprocesadores RISC por una serie de elementos únicos que no se encuentran en la definición base de este tipo de microprocesadores y que son añadidos propios que la diferencian del resto.

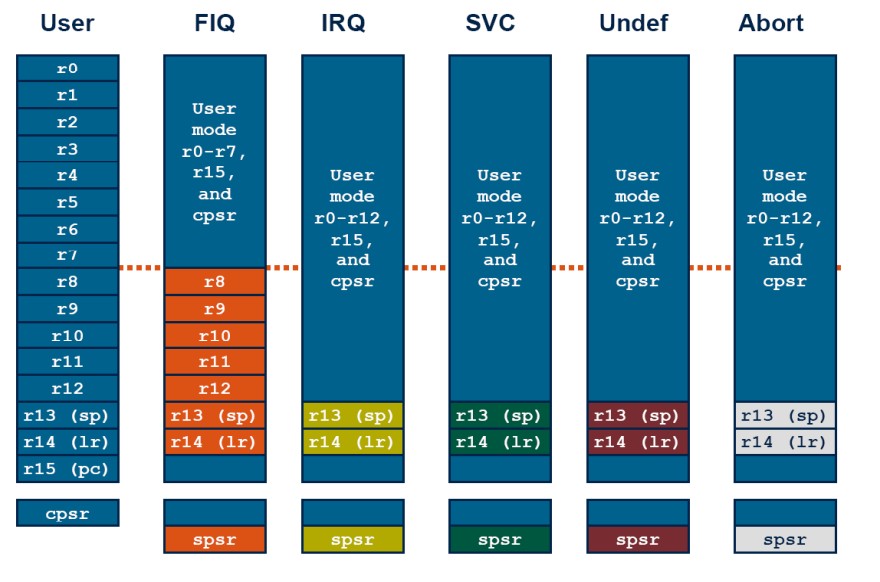

Registros

ARM dispone de 16 registros en total, 13 de los cuales (R0-R12) son de propósito general y pueden utilizarse libremente por parte del desarrollador, R13 tiene la función de puntero a pila, R14 la dirección de enlace a la subrutina actual y R15 es el contador de programa. Todos los registros pueden utilizarse bajo cualquier tipo de direccionamiento con la memoria, excepto los tres últimos cuya funcionalidad es fija e inamovible.

| Registro | Nombre habitual | Función | ¿Duplicado? |

|---|---|---|---|

| R0–R12 | — | 13 registros de propósito general. Se usan libremente. | De uso común para todos los modos. Escepto R8-R12 que se duplican en modo FIQ |

| R13 | SP | Stack Pointer (Puntero de pila). | Stack Pointer (Puntero de pila).. Se encuentra en cada modo excepto en los modos User y System. |

| R14 | LR | Link Register. Guarda la dirección de retorno cuando se hace una subrutina (BL). | Link Register. Guarda la dirección de retorno cuando se hace una subrutina (BL). Este registro se encuentra duplicado por cada modo. |

| R15 | PC | Program Counter. Guarda la dirección de la instrucción actual (más 8 bytes por efecto del pipeline). | Program Counter. Guarda la dirección de la instrucción actual (más 8 bytes por efecto del pipeline). Es común y compartido en todos los modos. |

No obstante, dependiendo del modo en el que se encuentre la CPU, el uso de los registros cambia.

En cuanto a los modos de funcionamiento de las CPU ARM, su definición y utilidad podéis verla en la siguiente tabla:

| Modo | ¿Para qué sirve? |

|---|---|

| User | Es el modo "normal", donde corre el código de los programas. Tiene pocos privilegios. |

| Supervisor (SVC) | Es donde corre el sistema operativo. Puede hacer cosas que el User no puede. |

| IRQ | Cuando ocurre una interrupción normal (como apretar una tecla), el procesador entra aquí. |

| FIQ | Igual que IRQ, pero más rápido. Se usa para interrupciones muy urgentes (como audio o vídeo). |

| Abort | Si el sistema intenta acceder a una zona de memoria inválida, entra en este modo. |

| Undefined | Si se ejecuta una instrucción desconocida, cambia a este modo. |

| System | Es como el Supervisor, pero usado cuando no se está manejando una excepción. |

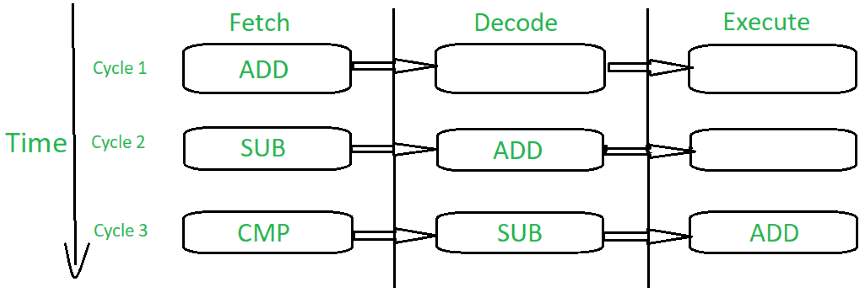

Contador de programa adelantado y pipeline

Una de las particularidades de toda CPU con set de instrucciones ARM es la forma en la que funciona el registro R15, el del contador de programa. abe destacar el hecho de que el Program Counter se encuentre 8 bytes por adelantado (4 en el caso de las instrucciones Thumb implementadas a partir de ARM7). Lo habitual es que este registro incluya la dirección de memoria actual, pero ARM hizo una trampa ya desde la primera CPU. El motivo de ello es que el pipeline de los chips ARM desde el ARM1 al ARM7 es de 3 etapas. ¿A qué se debe este desfase? Refleja el hecho de que el procesador ya ha leído (prefetch) las dos instrucciones siguientes. Es un comportamiento único de ARM que debe tenerse en cuenta, especialmente en programación, en ensamblador o al manipular direcciones de código directamente.

Todas las CPU ARM, hasta el ARM9 operan con un pipeline con las 3 etapas clasicas (fetch-decode-execute) y no fue hasta el ARM9, por influencia del StrongARM de Digital Equipment Corporation, que no se salto a un pipeline de 5 etapas añadiendo dos de ellas al final: memory y write. Las cuales se dan cuando la instrucción ha de acceder a memoria y escribir el resultado. Por lo que el Fetch de la siguiente instrucción se da simultáneamente a cuando la etapa memory de la actual se esta ejecutando. Por lo que los dos pasos adicionales son un desglose de la etapa execute en realidad.

Load/Store

Con tal de simplificar el diseño y con ello el consumo energético de las CPU con arquitectura ARM, uno de los sacrificios que tuvieron que hacer respecto a varias instrucciones que requieren cargar información en varios registros de propósito general a la vez, pues simplificarlos para que solo se pueda modificar un registro por ciclo de reloj.

Esto hace que ciertas instrucciones tengan un tiempo de ejecución más largo de lo habitual en un microprocesador RISC.

- Por un lado, tenemos las instrucciones LDR y SRT, las cuales modifican un registro de propósito general de la CPU por ciclo de reloj.

- Cuando se necesitan modificar varios registros al mismo tiempo se emplean las instrucciones LDM y STM, cuya velocidad dependerá de la cantidad de registros a modificar.

Esto permite a nivel de código fuente poder realizar el cambio de registros múltiple con una sola instrucción, lo que hace el código más compacto, pero a cambio de saltarse la regla de un solo ciclo de ejecución de las arquitectura RISC.

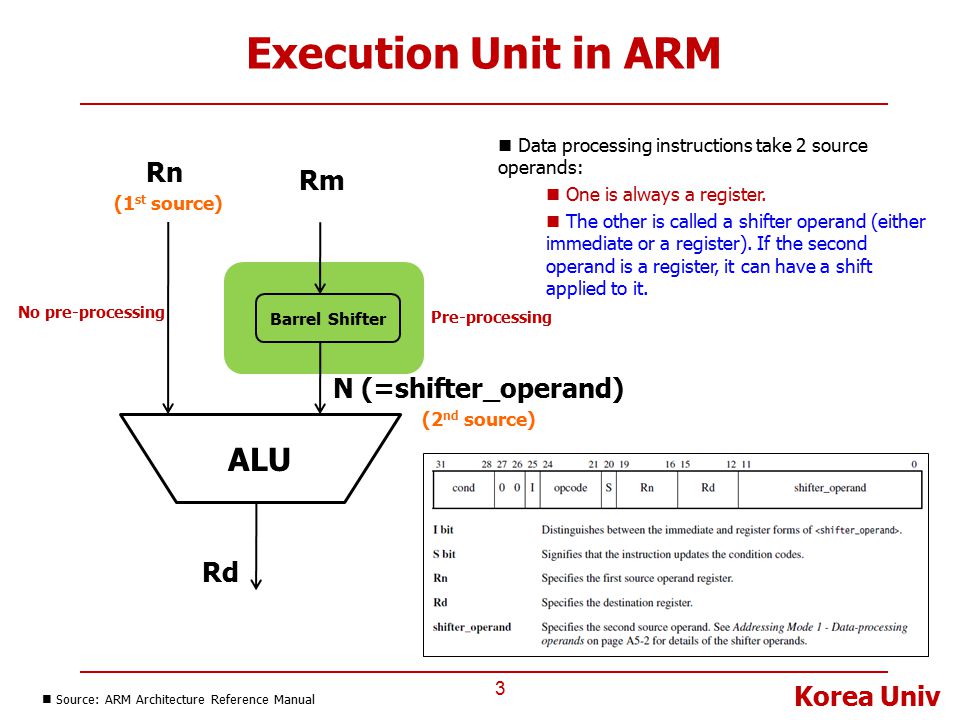

Barrel Shifter

Una de las particularidades que tienen las CPU ARM desde el primer diseño y que lo hacía mejor en este aspecto que muchos microprocesadores RISC de la época es el hecho de integrar un Barrel Shifter de serie. Esto es algo que en el caso de otros microprocesadores no se vio integrado de serie hasta el 386 de Intel, como curiosidad, el desplazamiento de los alienígenas de Space Invaders se conseguía a través de un Barrel Shifter implementado con chips TTL. Su nombre se debe a que está diseñado para desplazar varios bits de datos al mismo tiempo o en masa.

Estos se usan en electrónica digital y sistemas informáticos para realizar una amplia gama de operaciones, incluyendo cálculos aritméticos, manipulación de datos y cálculos de direcciones. Son conocidos por su velocidad y eficiencia, ya que pueden realizar múltiples operaciones de desplazamiento en un solo ciclo de reloj. Siendo clave en ARM para poder ejecutar ciertas instrucciones a mayor velocidad incluso que otras arquitecturas de filosofía RISC.

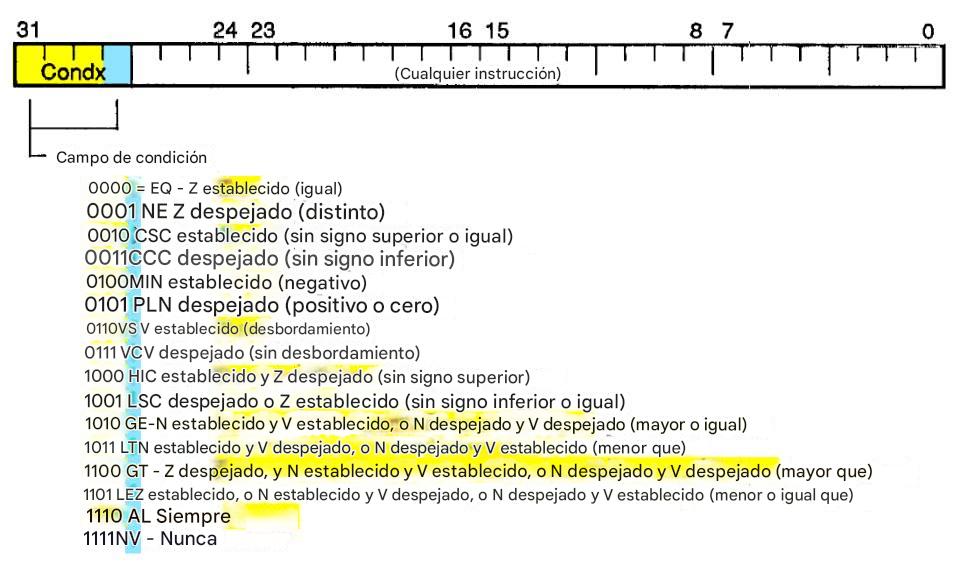

Todas las instrucciones son condicionales

Si bien esta particularidad desapareció en la octava generación del set de instrucciones, precisamente en la implementación a 64 bits de la arquitectura, es que todas las instrucciones son condicionales, los 4 primeros bits indican si una instrucción se ha de cumplir o no si sigue una condición concreta.

Esto se hace a través de los registros de estado (flags) que se activan en toda CPU cuando se da una condición especial. Se trata de otro de los trucos añadidos en la arquitectura ARM y en su set de instrucciones para recortar el tamaño del código fuente y ocupar menos espacio en memoria. Por cierto, los 4 bits se integran dentro de los 32 bits de tamaño de las instrucciones y no son supletorios. Se trata de los 4 primeros bits que lee el decodificador y si las condiciones que pide no se cumplen, simplemente ignora la instrucción y salta a la siguiente, lo cual se traduce en que todas las instrucciones ARM se ejecutan condicionalmente.

Consumo energético reducido

Desde sus inicios, uno de los objetivos clave en el diseño del chip ARM fue minimizar su consumo energético. El equipo liderado por Sophie Wilson y Steve Furber se propuso que el microprocesador no disipara más de 1 vatio de calor. Esto no solo era una meta de eficiencia, sino también una decisión pragmática: limitar el calor permitiría usar encapsulados de plástico estándar, mucho más económicos que los metálicos o cerámicos empleados en otros chips de mayor consumo.

Lo que comenzó como una elección de coste se convirtió, sin que lo supieran en ese momento, en una seña de identidad de la arquitectura ARM: la eficiencia energética extrema.La anécdota que marcó este logro llegó cuando ensamblaron y probaron el primer prototipo del ARM1. Al conectar el tester para medir el consumo, los ingenieros se llevaron una gran sorpresa: el amperímetro marcaba cero. Por un instante, pensaron que el chip no funcionaba. Sin embargo, el procesador operaba correctamente.

La razón detrás de este fenómeno era inesperada: los pines de alimentación no estaban correctamente conectados. Aun así, el ARM1 funcionaba porque recibía energía indirectamente a través de las señales de entrada de otros chips conectados a la misma placa. Esas señales pasaban por los diodos de protección del chip ARM, que normalmente se usan para evitar daños por sobretensión. En este caso, esos diodos actuaban como una fuente accidental de alimentación.

Este episodio, además de resaltar la eficiencia del diseño, dejó claro que el consumo del ARM era tan bajo que podía arrancar “por accidente”. Esa ligereza energética no solo resolvía un problema térmico y de costes, sino que también marcaría el camino de ARM como la arquitectura ideal para dispositivos portátiles y sistemas embebidos.