Si bien la gama TMS340 no llegó a usarse en ninguna consola de videojuegos, si que fue uno de los chips más prolíficos en el mundo de los videojuegos, especialmente por su uso en las máquinas recreativas de la empresa Midway, en especial se utilizó en títulos como la saga Mortal Kombat, Smash TV, Battletoads, NARCS y muchos otros títulos que aparecieron en los salones arcade. Aunque también se le recuerda por su uso en Hard Drivin de Atari, considerado el primer juego de carreras en 3D con gráficos poligonales de la historia y por el hecho de convertirse casi en un estándar gráfico en ordenadores.

Los orígenes de la serie TMS340

Si bien el TMS9918A es uno de los chips más famosos, las aportaciones de Texas Instruments no terminan ahí. Es más, el VDP diseñado por Karl Guttag es recordado por ser el primer chip gráfico con memoria propia, no obstante, tenía un punto débil, el cual no era otro que requería que la CPU accediera a la memoria local a través de los pines del propio TMS9918A, algo que impedía manipular los gráficos a tiempo real. Tampoco era necesario en un sistema tan primitivo, pero resultaba en un problema para crear un búfer de imagen completo donde cada píxel es definido por s valor y es que en el poco tiempo que la CPU podía enviar la información, como mucho se podía conseguir esto.

Es decir, la empresa no tenía un chip como el NEC 7220 para el mercado CAD/CAM, el cual era totalmente profesional y donde se manejaban grandes cantidades de dinero, por lo que Texas Instruments decidió crear su propia respuesta e ir más allá. ¿La idea? Crear una CPU con instrucciones y registros adicionales que le permitieran funcionar también como coprocesador y como chip gráfico dedicado. ¿El objetivo? Crear el primer chip gráfico totalmente programable, tanto es así que se pudiera utilizar como una CPU y dentro de la familia TMS3X0, la cual estaba compuesta por:

- Los DSP TMS320.

- La familia de procesadores TMS340, los cuales actuaban como CPU y chip gráfico.

- El TMS360 como controladora de disco duro, no fue aceptado por nadie.

- El TMS380 para conexiones de red local vía Ethernet.

El objetivo no era el mercado doméstico, es más el TMS340 no se ideo como un sucesor del TMS9918A y tampoco soporta rutinas de scroll, ni de sprites por hardware, más que nada por el hecho que tiene la suficiente potencia como para ejecutarlo por software y no sudar por ello. Tal fue la potencia del chip que encontró su lugar por parte de la empresa Williams, más tarde comprada por Midway y su recreativa NARC, la cual ofrecía gráficos al nivel de un System 16, pero teniendo un solo chip para gráficos y CPU, precisamente un TMS34010

Excepto para el audio, la placa arcade NARC, la Midway/Williams System Y utilizaba el chip de Texas Instruments como CPU y al mismo tiempo para generar los gráficos en pantalla y lo hacía por software. Para que os hagáis una idea es como si a día de hoy alguien sacara una CPU con la suficiente potencia como para prescindir de una Radeon o una GeForce, y no, no hablamos de que tendría una GPU integrada, sino que los propios núcleos de la CPU serían capaces de correr la lógica del juego y generar los gráficos, solo que aquí hablamos de un único núcleo.

La memoria VRAM y la serie TMS340

Sin embargo, uno de los mayores puntales del TMS34010 era el hecho de que no solo soportaba memorias tradicionales como DRAM y ROM convencionales como el resto de CPU, sino que su controlador de memoria integrado en el chip, veinte años antes de que Intel y AMD integraran uno en sus CPU para PC, tenía la capacidad de soportar un tipo nuevo de memoria, inventada por el mismo equipo de desarrollo del chip y lanzada dos años antes al mercado. Hablamos de la 4161 o VRAM que se lanzó en 1984 junto al c0ntrolador de memoria TMS34061 que permitía a otros chips usar este tipo de memoria, no obstante, esta se diseño para su uso con el TMS34010 y tenía una capacidad por chip de 64 Kbits (8KB) con un bus de 1 bit por pixel.

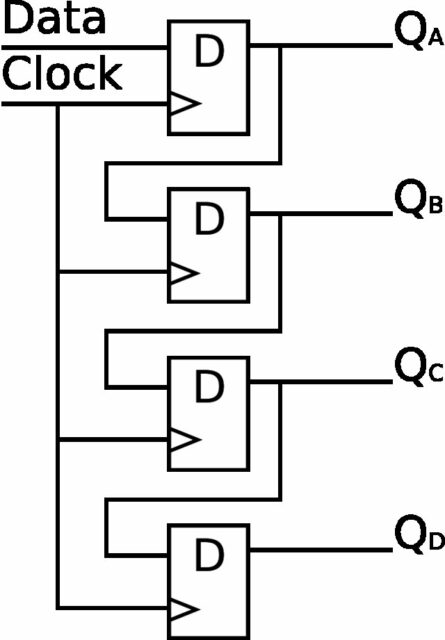

El problema de la memoria DRAM convencional, es que la mayoría de los accesos durante el tiempo de dibujado en pantalla se usaban para que el subsistema de vídeo leyese la información para enviarla al monitor, lo que virtualmente no le daba acceso a la CPU a poder actualizar la información en pantalla excepto en el periodo VBlank que solía ser de unas pocas decenas de líneas. La forma de solucionarlo por parte del equipo de Karl Guttag fue añadir un registro de desplazamiento de 256 bits dentro del chip. Más tarde lanzaron la segunda generación de la VRAM que aunaba cuatro chips 4161 en uno solo, con cuatro registros de desplazamiento y cuatro bits de salida.

¿Qué es un registro de desplazamiento?

Pues se trata de un circuito secuencial que almacena una cantidad concreta de información y en cada ciclo de reloj, desplaza el contenido 1 bit a la izquierda o la derecha, introduciendo un nuevo bit y enviando a través del pin de salida el ultimo bit de la cadena. Hemos de partir del hecho de que para poder dibujar con la suficiente velocidad, se le han de enviar al DAC del monitor un flujo continuo de bits (información de los pixeles) a una frecuencia lo suficientemente alta. Como hemos dicho esto se puede hacer en las memorias convencionales, pero cerrando el flujo de contacto con el chip gráfico o la CPU mientras se dibuja.

La VRAM durante el HBLANK en el que el haz de electrones se reposicionaba en la siguiente línea copiaba la información de la misma como si fuese un búfer de línea en el registro de desplazamiento, para ir goteando bit por bit hacía la circuitería encargada de generar los pixeles en pantalla y la lógica de color a la velocidad que requiere la salida de vídeo. Esto liberaba la presión sobre la memoria DRAM dentro de la VRAM, permitiendo a la CPU acceder en cualquier momento de la etapa de dibujado y sin verse limitada al acceso durante el periodo VBlank, lo que permitía realizar trucos a través de cambiar ciertos valores en la memoria de vídeo mientras hubiese tiempo para ello, todo por el hecho que mientras que la salida de vídeo estaba enviando la actual línea a pantalla, la CPU podía acceder a la memoria de vídeo.

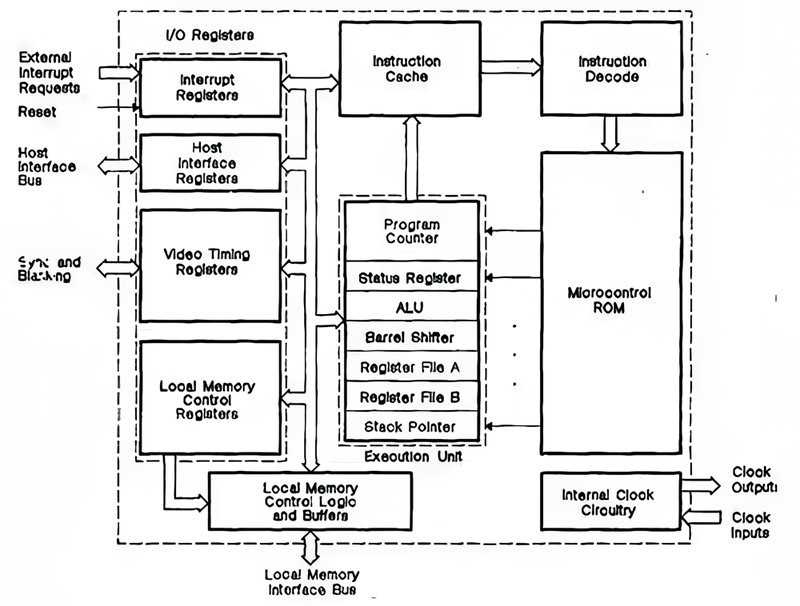

El TMS34010

En 1986 Texas Instruments lanzó el TMS34010, un chip que podía hacer tres funciones distintas:

- Funcionar como una CPU completa, hasta el punto en que tenía la capacidad para poder compilar y ejecutar un programa escrito en lenguaje C. Su rendimiento bruto era impresionante, teniendo una potencia de 6.25 MIPS, tened en cuenta que un 68000 a 8 MHz alcanzaba 1 MIPS.

- Poder funcionar como coprocesador, ya sea como una segunda CPU en modo subordinado con su memoria, para ello tenía una interfaz directa de 16 bits que permitía el contacto directo entre ambos chips.

- Exclusivamente como chip gráfico, donde también utilizaba la interfaz de comunicación directa. Esto le permitía adaptar el chip para usarse en multitud de sistemas, por ejemplo se vio en tarjetas gráficas no solo para los PC AT y posteriores (TIGA), sino también para Commodore Amiga, Atari ST e incluso estaciones de trabajo avanzadas.

Por no hablar de su uso en videojuegos tal y como os hemos comentado antes. Sin embargo, se trataba de un chip único en su especie, ya que trajo consigo un set una serie de registros e instrucciones optimizados para la generación de gráficos en pantalla. Por un lado, el set de registros A que se trataba de 15 registros de propósito general de 32 bits. Que por cierto, se nos ha olvidado decir que el TMS34010 era un chip de 32 bits, al menos en lo que a las unidades de ejecución se refiere y a los registros del set A, luego disponía del clásico registro de estado con los FLAGS y que es indispensable en toda CPU y puntero a pila que era compartido entre ambas funcionalidades.

El punto débil del chip era su interfaz de memoria, la cual era triple multiplexada, debido a que el sistema maneja direccione de memoria de 32 bits, pero solo tiene 16 pines lo que hace es primero transmitir la fila, luego la columna y una vez se ha hecho la sincronización se envié en dos pulsos los 32 bits de datos. Esto hacía que cualquier acceso a memoria requiriese 8 ciclos de reloj durante la captación, luego el decodificar le añadía un ciclo de reloj adicional y luego lo que tardase cada instrucción. Sin embargo, esto lo compensaba con una velocidad de reloj extremadamente alta para la época: 50 MHz.

Pero estos 8 ciclos son solo la base:

- Si la instrucción no está en la caché de 256 bytes, los ciclos mínimos suben a 11.

- Además, cada instrucción puede necesitar varios accesos adicionales a memoria y ciclos internos de la ALU.

En otras palabras, el rendimiento por MHz del TMS34010 es relativamente bajo, y si funcionara a la misma frecuencia que un 68000, sería extremadamente lento. Por eso se decidió aumentar su frecuencia interna: para compensar la latencia del bus y los múltiples ciclos de memoria. Además, de requerir una gran cantidad de ciclos de reloj para ejecutar las instrucciones gráficas a la suficiente velocidad.

Registros gráficos

No obstante, el punto fuera del TMS34010 era su capacidad de funcionar como chip gráfico totalmente programable, en el sentido que en vez de colocar unos datos en una partes concretas de la memoria, lo que se podía hacer era escribir un programa completo que le dijera como generar los gráficos en pantalla y el TMS34010 lo generaba. Para ello utilizaba una serie de instrucciones gráficas y registros, los cuales le daban la misma versatilidad para ello que otros sistemas de su época como el chipset del Commodore Amiga o el NEC 7220, pero con la particularidad de que aquí no hablamos de un chip gráfico dedicado.

| Registro GSP | Nombre | Tamaño / Formato | Descripción |

|---|---|---|---|

| B0 | SADDR | 32 bits: lineal (32) o 2D (16+16 X,Y) | Contiene el puntero de dirección del arreglo fuente para operaciones PIXBLT. Se ajusta automáticamente para esquinas si es necesario. En LINE contiene la variable de decisión actual. |

| B1 | SPTCH | 32 bits (entero múltiplo de 16) | Diferencia lineal entre las direcciones de inicio de líneas adyacentes del arreglo fuente en instrucciones PIXBLT y FILL. Permite moverse de fila a fila y puede estar restringido a potencias de dos en algunos casos para direccionamiento XY y ajuste automático de esquinas. |

| B2 | DADDR | 32 bits: lineal (32) o 2D (16+16 X,Y) | Contiene el puntero de dirección del arreglo destino para PIXBLTs. Ajuste automático para esquinas si es necesario. En LINE contiene la dirección XY del siguiente punto DDA. Se usa con DYDX para rectángulos comunes. |

| B3 | DPTCH | 32 bits (entero múltiplo de 16) | Diferencia lineal entre las direcciones de inicio de líneas adyacentes del arreglo destino en PIXBLT y FILL. Permite moverse de fila a fila y puede estar restringido a potencias de dos en algunos casos para direccionamiento XY y ajuste automático de esquinas. |

| B4 | OFFSET | 32 bits, lineal | Dirección lineal del primer píxel en el espacio XY (X=0,Y=0). Base para conversiones XY a lineal. No se modifica durante la ejecución de instrucciones. |

| B5 | WSTART | 32 bits, XY | Dirección XY del píxel menos significativo en la ventana de recorte de destino. Se usa con WEND, DADDR y DYDX para preclipping de píxeles y líneas. No se modifica por instrucciones. |

| B6 | WEND | 32 bits, XY | Dirección XY del píxel más significativo en la ventana de recorte de destino. Se usa con WSTART, DADDR y DYDX para preclipping de píxeles y líneas. No se modifica por instrucciones. |

| B7 | DYDX | 32 bits (16+16 DX,DY) | Especifica las dimensiones X (DX) y Y (DY) del arreglo de destino en píxeles. Usado junto con WSTART, WEND y DADDR para preclipping y operaciones de bloque. La mayoría de las instrucciones no modifican DYDX; algunas instrucciones con ventana pueden ajustar DYDX para el rectángulo común. |

| B8 | COLORO | 32 bits (16 bits usados) | Color de reemplazo para los bits 0 del arreglo fuente en PIXBLT B,L y PIXBLT B,XY. Los píxeles se alinean con los píxeles de destino; el valor de los 16 bits inferiores se usa como color de fondo. |

| B9 | COLOR1 | 32 bits (16 bits usados) | Color de reemplazo para los bits 1 del arreglo fuente en PIXBLT B,L y PIXBLT B,XY. Para FILL, DRAV y LINE, COLOR1 especifica el color a usar en los píxeles de destino a alterar. Los píxeles se alinean con los píxeles de destino en memoria. |

| B10–B14 | 32 bits | Se usan como operandos implícitos para la instrucción LINE y como registros temporales para PIXBLTs y FILLs. |

Para ello El TMS34010 disponía de un segundo set de registros (B), los cuales eran utilizados por las diferentes instrucciones gráficas que soportaba este particular chip, de esta manera no entraba en conflicto con el uso de las instrucciones de propósito general que corresponden al set de registro A. Por lo que el único registro compartido entre ambas partes era el puntero a pila o Stack Pointer.

Estos registros eran soportados por una serie de instrucciones implementadas en la CPU, las cuales utilizaban el set de registros B para funcionar.

- PIXBLT: permite copiar bloques de píxeles de un origen a un destino, con soporte para direcciones lineales o XY, ventanas de recorte y transformaciones de color (COLOR1/COLORO). Se usa para copiar imágenes o sprites completos de la memoria fuente a la memoria destino, con la posibilidad de cambiar colores o invertir el bloque. Por ejemplo, copiar un icono en la pantalla sin alterar el resto de la imagen.

- FILL: rellena un bloque rectangular de píxeles con un color específico. Funciona en arreglos bidimensionales y puede usar ventanas de recorte y dirección XY o lineal. Se utiliza para dibujar fondos sólidos o limpiar un área de la pantalla. Por ejemplo, rellenar un rectángulo con color azul para representar un panel de información.

- LINE: implementa el bucle interno rápido del algoritmo de Bresenham para dibujar líneas. Utiliza registros como DADDR y SADDR para determinar posiciones de píxeles y DYDX para el incremento en X e Y. Esto permite dibujar líneas rectas de manera eficiente. Por ejemplo, trazar bordes de un rectángulo o una cuadrícula en pantalla sin calcular cada posición de manera manual.

- DRAV (Draw and Advance): dibuja un píxel y avanza la dirección del píxel en una cantidad especificada. Permite implementar algoritmos incrementales para círculos, elipses, arcos y otras curvas.

- PIXT (Pixel Transfer): transfiere píxeles individuales de una ubicación a otra. Es útil para manipulación directa de píxeles cuando se requiere control detallado de la posición de cada píxel. Se utiliza cuando se necesita modificar píxeles de forma no uniforme o hacer efectos especiales, como transparencia selectiva o copiar píxeles no contiguos de una imagen a otra.

El truco del TMS34010

En una CPU, las instrucciones como las descritas en la sección anterior requieren una gran cantidad de ciclos de reloj para ejecutarse, esto se debe a que las ALU utilizadas en este tipo de chips están pensadas para realizar las operaciones aritméticas básicas, a partir de las cuales se construyen todas las demás. De ahí a que se necesitaran chips de apoyo como coprocesadores matemáticos que realizaban instrucciones aritméticas complejas en muchos menos ciclos de reloj. Sin embargo, el TMS34010 carecía de coprocesador matemático y esto obligaba a compensar a través de una alta velocidad de reloj, por eso el chip funcionaba a 50 MHz.

Es decir, el TMS34010 no es un hardware dedicado para gráficos, sino de una CPU convencional con algunos extras, y aquí hemos de tener en cuenta una serie de puntos importantes:

- El hardware dedicado suele implementar la operación completa de sus instrucciones en un solo circuito, lo que permite la ejecución de la instrucción en un ciclo de reloj, mientras que en la CPU la instrucción aritmética para ser más digerible se descompone en otras más sencillas. Es decir, implementan el algoritmo directamente en en el silicio.

- En una CPU, las instrucciones pasan por una serie de etapas que los lectores de HARDVERSO ya conoceréis. En un hardware dedicado dichas etapas se simplifican o incluso llegan a eliminarse, pudiendo concatenar varias instrucciones mucho más rápido.

La ventaja del TMS34010 era ser totalmente programable en comparación con otros chips de la época, lo cual es un hito histórico. Por eso el TMS34010 opera a 50 MHz, una cifra extremadamente alta para 1986. A ello hemos de sumarlo el ancho de banda necesario, ya que como chip gráfico, el TMS34010 debía mover información entre la CPU y la VRAM o DRAM a gran velocidad para escribir en el búfer de imagen sin retrasos.

El TMS34020

Dos años más tarde, en 1988, y bajo un empaquetado de 132 pines, casi el doble que el chip de primera generación, Texas Instruments lanzaba el sucesor del TMS34010, el llamado TMS34020, el cual mejoraba levemente la arquitectura y fue utilizado años después en las recreativas de Revolution X y Battletoads haciendo el mismo papel que su predecesor.

Obviamente el chip recibió diversas mejoras, la primera de ellas fue que su bus de memoria dejo de estar multiplexado respecto a datos y direccione, pero continuaba siendo de 16 bits en ambos casos, la segunda es que redujo el consumo a través de recortar su velocidad de reloj a los 40 MHz, pero también disminuyo la cantidad de ciclos de reloj necesarios para hacer ciertas instrucciones. Provocando que el rendimiento máximo pasará de los 6.25 MIPS a los 10 MIPS. También hubo mejoras en la caché de instrucciones que paso de ser de 256 bytes a 512 bytes, al igual que también introdujo algunas mejoras adicionales en forma de nuevas instrucciones y el uso de una VRAM mucho más avanzada.

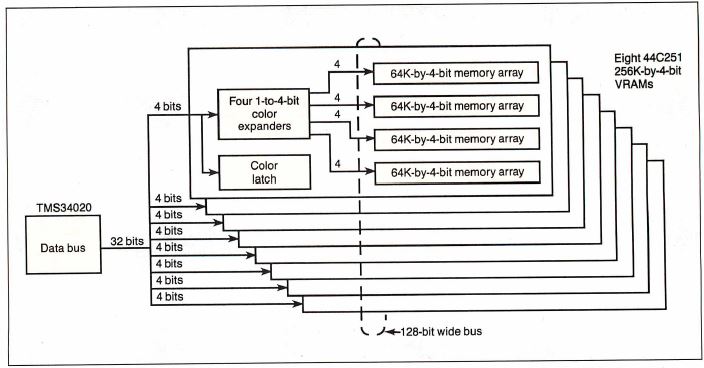

VRAM de tercera generación

En realidad, el TMS34020 nació en 1988, justo para aprovechar las capacidades de la tercera generación de memorias VRAM (44C251), las cuales tenían una organización interna de cuatro matrices de 256 Kbits (1 Mbit) con un bus de 4 bits por chip y con 4 registros de desplazamiento de 512 bits cada uno. Esto se traducía en que cada chip podía transmitir hasta 4 bits por pixel en modo packed pixel o 4 planos de bits. Por ejemplo, las primeras VGA utilizaros dos chips 44C251 como memoria de vídeo, lo que le permitía alcanzar su configuración de 256 KB con hasta 256 colores por pixel. Sin embargo, Texas Instruments lo diseño para aprovechar las capacidades del TMS34020.

Una de las mejoras era el Block Write Mode, en el que cada chip de memoria tenía un registro interno de color. Pues bien, en el modo BWM, lo que se hacía era ignorar los 2 bits menos significativos de la dirección, de esta manera la dirección de memoria apuntaba en realidad a 4 posiciones consecutivas. ¿El resultado? Los 4 pines de datos ya no cargaban el color, sino que funcionaban como simples mascaras de escritura donde un 1 escribía el color en esa posición de pantalla, un 0 dejaba la posición sin tocar. Gracias a ello era posible escribir rectángulos o zonas de un único color sólido muy rápido.

Se añadieron dos nuevas instrucciones en el caso del TMS34020 que permitían tomar ventaja del modo BWM de la VRAM de tercera generación. El VFILL que permitía rellenar zonas de pantalla con un solo color con una tasa de relleno cuatro veces superior, mientras que VBLT permitía tomaba un bitmap en monocromo , donde el valor del color era el mismo que el del registro de color. Lo cual permitía dibujar patrones de bits sobre la memoria de vídeo sin tener que leer, modificar y escribir de nuevo en memoria, sino hacerlo en un solo ciclo.

TIGA

Dado que el TMS34020 era totalmente programable, hasta el punto en que era posible ejecutar un programa en C con el mismo, incluso para generar gráficos en pantalla, la gente de Texas Instruments diseño una interfaz de software, es decir, una API gráfica, a la cual bautizaron como Texas Instruments Graphics Architecture (TIGA). Dicha API era independiente de resolución y profundidad de color, al contrario que estándares como el VGA cuyas especificaciones estaban fijas, lo que permitió el uso durante varios años del GSP, en especial en el mercado de las tarjetas gráficas profesionales de alta gama para plataformas como el PC e incluso el Commodore Amiga.

Su popularidad fue tal que se convirtió en la tarjeta gráfica de referencia para aquellos que en PC trabajasen en el diseño asistido por ordenador y también en las primeras aplicaciones de diseño gráfico complejas. No obstante, TIGA no fue adoptado por culpa de Microsoft, lo que le otorgo la victoria en el mercado a Super VGA que termino por ser el estándar gráfico en PC, pese a que el TMS34010 podía ejecutar gráficos con calidad SVGA más que de sobras, el problema era la forma en la que Windows manejaba los gráficos en pantalla, la cual era a través de comandos de bajo nivel con una gran cantidad de sobrecarga. En cambio, el GSP estaba diseñado para ejecutar un programa gráfico de forma directa para dibujar el frame en pantalla. Esta disparidad en la filosofía hizo que según Karl Guttag, bajo Windows 3 en adelante, el sistema operativo dejase sin hacer nada al chip más del 90% del tiempo, dándole la oportunidad a brillar a chips más baratos y simples.

El tiempo le dio la razón a Texas Instruments

El hecho de no tener una API gráfica en condiciones fue lo que entre otras cosas y con el advenimiento de los gráficos en 3D una gran cantidad de fabricantes siguieran los pasos de Texas Instruments con TIGA y crearan sus propias API gráficas, como por ejemplo 3Dfx Interactive con Glide. Por desgracia, cuando esto ocurrió el TMS34010 ya se encontraba totalmente enterrado en el pasado, pero el chip tuvo su época dorada a finales de los 80 y principios de los 90, por lo que aunque no se convirtió en un estándar fue un chip adelantado a su tiempo y su influencia es suficiente como para que le hayamos dedicado una entrada.