El MOS 6502 es la CPU con la que se inició la informática doméstica y el primero en usarse a gran escala en consolas y ordenadores que se podían encontrar en las tiendas. Fue utilizado además en multitud de sistemas distintos en los años 80 y 90, es por ello que le hemos dedicado este artículo, el cual podrás utilizar como consulta, en él te explicaremos cómo funciona la arquitectura de este chip, así como las diferentes versiones de este chip.

¿Qué es el MOS 6502?

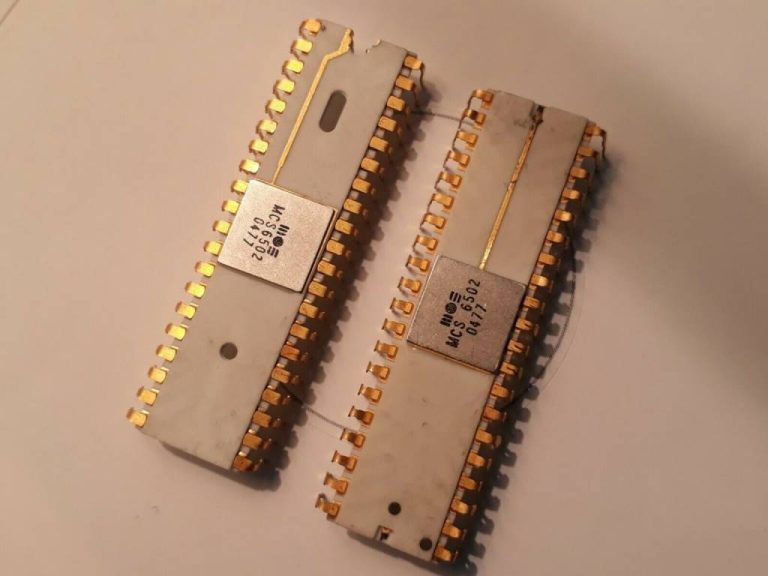

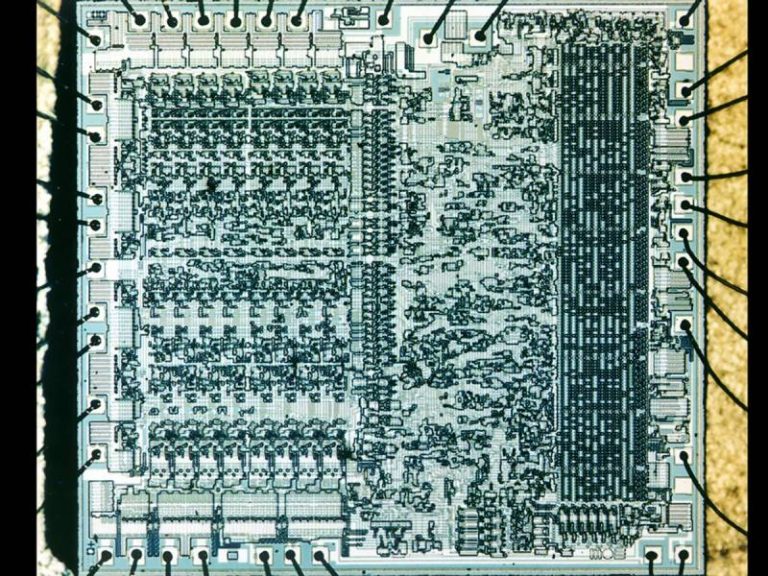

El MOS 6502 es una CPU de 8 bits diseñada por Chuck Peddle, quien ya había trabajado antes en el diseño del 6809. Se creó inicialmente no para ser el microprocesador de un ordenador personal, sino como microcontrolador de sistemas autómatas a nivel industrial. Sin embargo, este se vendía en 2 chips distintos, siendo uno de ellos la propia CPU y el otro el resto de la circuitería.

e trata de una CPU de 8 bits con un direccionamiento de hasta 16 bits, lo que significa que sin ayuda de chips de mapeo de memoria puede acceder hasta a 64 KB de memoria RAM. No obstante, se diferencia de sus competidores por ser un diseño mucho más simple que otras CPU de su época, pero no menos funcional, no en vano, esto les permitía venderlo a un precio mucho más bajo que la competencia, lo que permitió los primeros sistemas domésticos vendidos en masa en gran volumen: el Apple II y la Atari VCS, sin desmerecer para nada al Commodore PET.

Su diseño está pensado para funcionar a bajas velocidades de reloj, por lo que sus instrucciones tardan menos Hz en resolverse respecto a otras CPU. Por lo que suele igualar a otros microprocesador que van al doble de velocidad e incluso en algunos casos incluso hasta superarlos.

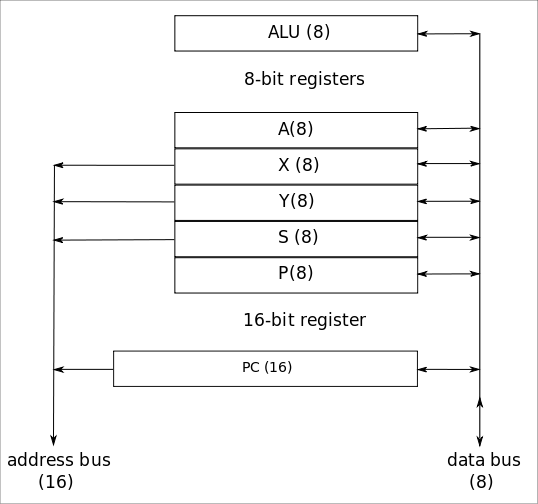

Registros en el MOS 6502

Los registros son memorias internas dentro de la CPU de pequeño tamaño y de latencia totalmente nula que se utilizan por parte del microprocesador para realizar sus funciones elementales. Sin embargo, una cosa que diferencia el MOS 6502 del resto es que tiene la configuración mínima necesaria, careciendo por completo de registros de propósito general de libre uso para el desarrollador. No obstante, esta CPU compensa esta limitación de una manera única que es la llamada Page Zero que le permiten acceder a los primeros 256 bytes de memoria a una mayor velocidad que el resto.

El 6502 tiene un número de registros relativamente pequeño en comparación con las CPU de su misma era, esto hace que terminará siendo odiado por los programadores de sistemas, ya que hace que sea especialmente desafiante y un dolor de cabeza programar haciendo un uso de los registros y la memoria.

Contador de programa

El contador de programa (PC o Program Counter) es un registro de 16 bits que apunta a la siguiente instrucción a ejecutar. Este incrementa en 1 en cada instrucción, excepto cuando es una instrucción de salto donde se copia la información del registro acumulador a este registro para que el MOS 6502 empiece a ejecutar desde la nueva drección de memoria. También se puede ver modificado por el mecanismo de interrupciones, momento en que se ejecutará la rutina de gestión de las mismas que se encontrará en algún punto de la ROM del sistema.

Stack Pointer

El MOS 6502 asigna una pila de 256 bytes de tamaño entre las direcciones de memoria $0100 y $01FF. Sin embargo, el registro de puntero a pila (S o Stack Pointer) permite desplazar el inicio de la pila en unas 256 direcciones de memoria, dado que este es de 8 bits. Dicha pila se gestiona con las instrucciones PUSH y POP y funciona como una pila de platos o mecanismo LIFO (Last In First Out), es decir, el último dato en entrar será el primero en salir. La CPU no tiene ningún mecanismo de gestión de pila, por lo que si esta supera los 256 bytes de tamaño y provoca un overflow puede llevar a errores fatales en el programa.

Acumulador

El registro Acumulador (A) se utiliza en todas las operaciones aritméticas y lógicas realizadas por la ALU, la única excepción son las operaciones de incremento y decremento. El contenido del acumulador se obtiene o se almacena directamente de la RAM, ya sea de forma convencional o utilizando la pila y su tamaño es de 8 bits.

Registros índice (X e Y)

A la hora de acceder a la RAM se utilizan los registros de índice X e Y. En realidad tenemos 256 páginas de 256 bytes cada una. Si se usa solo el registro X, entonces el acceso a memoria se hace en la página cero, que son los primeros 256 bytes de memoria. La cual es la parte de la memoria más rápida y cualquier instrucción que use variables almacenadas en esta sección de memoria se ejecutará en un ciclo de reloj menos. En cuanto al registro Y, tiene una funcionalidad adicional, si no se usa para el acceso a memoria se puede utilizar como registro contador.

Flags o registros de estado

El registro de estado o FLAG es un tipo de registro común en todas las CPU, se trata de una serie de bits que se activan cuando se dan ciertas condiciones, sin embargo, hay que tener en cuenta que si bien algunos bits de estado son comunes, otros, en cambio, son únicos de cada microprocesador y no todos tienen la misma cantidad de estos. En el caso del MOS 6502 es un registro de 8 bits, cuyos bits indican lo siguiente:

- Acarreo (C): este bit se indica cuando hay acarreo en una operación aritmética.

- Cero (0): se activa cuando el resultado de una operación es cero, es especialmente útil para activar saltos cuando se hace una comparación entre dos números como causante de la misma.

- Desactivar las interrupciones (ID): si este bit está activo, el MOS 6502 ignoras las peticiones de interrupción realizadas por los periféricos a la CPU.

- Modo decimal (BCD): activa el modo decimal, por lo que la CPU deja de operar en modo binario a hacerlo de forma decimal.

- Ruptura (BRK): se activa cuando se utiliza la instrucción BRK para finalizar abruptamente un programa. Tras activar este bit se genera un proceso de interrupción que gestionará el proceso de salida del programa, ya sea una rutina simple o a través del sistema operativo.

- Overflow (O): este bit se activa cuando el número resultante es más alto que el que puede almacenar el registro acumulador.

- Negativo (N): el bit indica si el primer bit almacenado en el acumulador indica una cifra o un símbolo de positivo o negativo. En el primer caso, almacena un número entre el 0 y el 255, en el segundo caso entre el -127 y el 127.

Acceso compartido a la RAM

La gran mayoría de sistemas basados en el 6502 no se diseñaron realmente alrededor de esta CPU, sino que esta fue adoptada por ser más barata que el Z80. Y esto es importante para entender ciertos problemas de rendimiento en ciertas arquitecturas. En su concepción original, el 6502 estaba pensado para compartir la misma RAM que los procesadores de apoyo. Por lo que configuraciones basadas en chips con su propia VRAM, como es el caso de la PPU de Famicom/NES son diseños inicialmente pensados para un Z80 trasladados a un 6502.

La trampa del MOS 6502 es que su velocidad de reloj era muy baja, esto permitía tener chips de memoria a igual o al doble de velocidad. Por ejemplo el Apple I y el Apple II usaban RAM a 2 MHz con la CPU a 1 MHz y el sistema de vídeo a 1 MHz y lo que hacían era acceder de forma alterna. Para ello, el propio 6502 duplicaba de forma invertida la señal de reloj y con ello controlaba los tiempos del chip de vídeo. Lo cual sirve para construir sistemas mucho más simples, al poder usar la RAM del sistema también como VRAM sin pérdida de rendimiento.

Este método de acceso a la RAM fue clave para la creación de los primeros ordenadores personales, dado que supuso un ahorro importante en los costes a la hora de implementar el sistema de vídeo con menos chips de memoria. No obstante, hemos de tener en cuenta que no todos los sistemas basados en el 6502 utilizan esta forma de organizar la RAM.

Variantes del MOS 6502

Con el tiempo fueron apareciendo variantes del MOS 6502, algunos de ellos exclusivos de ciertos sistemas y otras evoluciones naturales del mismo, pero todos ellos basados en la misma arquitectura que el chip original, es por ello que hemos decidido enumerarlos todos, así como los diferentes sistemas en los que fueron integrados.

Sally (6502C)

Una variante creada por Atari que incluía un pin adicional HALT (parada) que detenía la CPU por completo para dejarle acceso a la RAM al ANTIC en los sistemas de 8 bits de la empresa con el hardware derivado del Atari 800 como son el Atari 5200 y la serie Atari Xe.

Dicho cambio le permite a la unidad DMA integrada en el ANTIC tomar acceso a la RAM del sistema en cualquier momento, parando por completo la actividad de la CPU, la cual se reanudará donde lo dejo tan pronto como la señal del pin HALT cambie de polaridad

MOS 6510

CBM de cara a la creación de su Commodore 64 creo una variante del 6502 mejorada con los siguientes cambios. Su velocidad de reloj puede ser de 1 MHz (C64) o de 2 MHz (C128) donde recibe el nombre de 8502. Es muy parecido en funcionalidad al 6502C, dado que añade también un pin de parada (HALT), solo que es nombrado como AEC en el caso del 6510. ¿Su utilidad? Le permite a la unidad DMA integrada en el VIC-II, tomar acceso a la RAM, por lo que es la misma utilidad que la variante de Atari.

Sin embargo, el mayor cambio es el añadido de una serie de pines adicionales que permiten comunicar la CPU con los periféricos de forma directa, para un mayor detalle de cómo funciona os relatamos a nuestro artículo sobre el hardware del Commodore 64.

Ricoh 2A03

El Ricoh 2A03 es una variante del MOS 6502 creada por Ricoh para Nintendo y que se uso en la consola Famicom, así como su variante occidental, la Nintendo Entertainment System o NES. Se trata de una versión no licenciada, pero con una serie de cambios bastante profundos. En cuanto a su velocidad de reloj, esta funciona a 1.79 MHz.

Esta variante del 6502 tiene dos cambios importantes, para empezar carece del modo decimal, por lo que las instrucciones correspondientes al mismo, así como toda la circuitería que lo hace posible, se ha visto eliminado. Sin embargo, los opcodes del chip original de MOS siguen estando allí. La otra mejora es el añadido de un generador de audio programable, o chip de sonido, dentro de la misma CPU, el cual dispone de los siguientes canales:

- Dos canales de onda cuadrada.

- Un canal de onda triángulo.

- Un canal de ruido.

- Un canal PCM.

Para manejar el audio, el 2A03 dispone de 22 registros en memoria adicionales, curiosamente dos de ellos se utilizan para gestionar el gamepad de la consola.

WDC 65C02

Una variante creada con transistores CMOS por Western Digital, hay que partir del hecho que el MOS 6502 original se creó utilizando transistores NMOS y el 6510 del tipo HMOS. Es la variante estándar más utilizada a dia de hoy fuera de los diseños exclusivos y puede operar entre los 1.2 MHz y los 14 MHz. Al igual que Z80 respecto al 8080, se puede considerar como una versión avanzada, ya que añade una serie de instrucciones adicionales que no se encontraban en la CPU original.

La versión original del chip se lanzó en 1983, siendo el Apple IIc Portable el primero en integrarlo, su mayor ventaja era un menor consumo respecto al chip original y el poder alcanzar velocidades de reloj más altas. Pero principalmente se diseñó como una versión para sistemas de bajo consumo energético, tanto es así que termino siendo la CPU de la Atari Lynx.

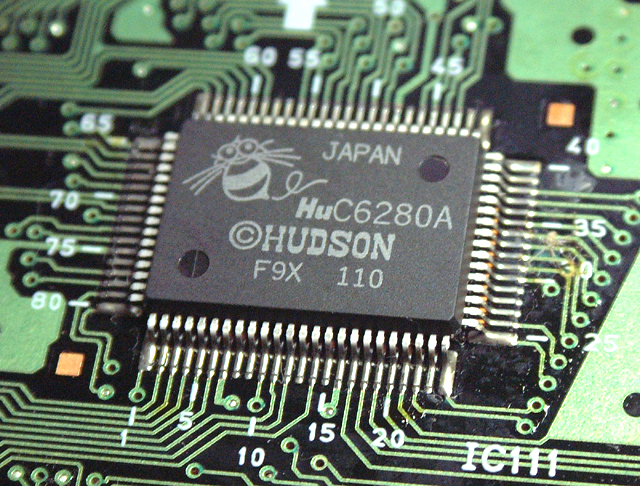

HU6280A

Se trata en este caso de una variante del 65C02 fabricada por NEC y creada por Hudson Soft para la consola PC-Engine/TurboGrafx. Puede funcionar tanto a 1.79 MHz como a 7.16 MHz y se trata de una de las versiones más avanzadas del 6502, ya que no solo hereda las instrucciones del 65C02, sino que además añade otras adicionales que son exclusivas de este diseño.

Su cambio más importante es el añadido de un mapeador, esto le permite pasar de manejar 256 páginas de 256 bytes cada una a la misma cifra de páginas de 8 KB de tamaño cada una. Además, tiene 8 KB de memoria interna en la CPU, lo que permite acelerar el tiempo de ciertas instrucciones y es clave para hacer funcionar este microprocesador a 7.16 MHz. Lo cual le convierte, pese a operar solo con números de 8 bits, en la CPU más rápida de su generación, por encima incluso que el 68000 a 12 MHz de Neo-Geo y el MegaCD.

Otra de las novedades de esta variante del MOS 6502 es el añadido de un generador de sonido programable, al mismo estilo que el 2A03 de la Famicom/NES, pero de seis canales y funcionando a través de tabla de ondas. Por lo demás es exactamente igual al del 65C02 que os hemos descrito en la sección más arriba.

El siempre polémico 65C816

Entre las diferentes variantes del MOS 6502, el 65C816 de Western Digital, utilizado por primera vez en el Apple IIGS y posteriormente en la Super NES/Super Famicom bajo el nombre 5A22, pues es uno de los más polémicos. Más que nada por el hecho que muchos apuntan a que es una actualización menor del 65C02, cuando realmente no es así y tiene una serie de cambios importantes que suelen pasarse desapercibidos. Es más, su mala fama se debe más bien por la arquitectura de la consola de 16 bits de Nintendo que no por el propio chip en sí.

El motivo por el cual no le hemos dedicado un artículo aparte es simple, se trata de una evolución del 6502 y no es productivo para nosotros y tampoco para los lectores volver a escribir y a leer de nuevo buena parte de los conceptos ya descritos en este artículo. Desde nuestro punto de vista, de la misma manera que un 80386 pertenece a la familia de los 8086 por compartir set de instrucciones base y evolucionar uno a partir del otro, pues lo mismo se puede decir 65C816 respecto al 6502.

¿Por qué es menos querido que el 6502?

El primero de sus puntos negativos está en el hecho que WDC quiso mantener el chip en un encapsulado de 40 pines y es por ello que el bus de este chip es de 8 bits. Es decir, necesita dos ciclos de instrucción para leer o escribir datos de 16 bits en vez de uno solo. Si bien sus accesos a memoria son mucho más rápidos que el Motorola 68000, el Zilog Z80 y los 8086 y 80286 de Intel. Dicho bus es visto como una limitación a un diseño que mejora enormemente al MOS 6502.

El otro problema es su integración en la Super NES como CPU principal. Todos los 65XX necesitan operar con memorias iguales o más rápidas respecto a su velocidad de reloj. Dado que si esto no es así ocurre contención. En la consola de 16 bits de Nintendo tenemos el problema de ROMS en cartuchos con una velocidad paupérrima, que acaban añadiendo ciclos de reloj por instrucción. Y dado que dicha consola es el hardware más conocido con este microprocesador, se ha llevado la mala fama por el camino.

Por si fuese poco, el 65816 puede alcanzar velocidades de reloj mucho más altas de las que alcanza en SNES, justo las mismas que la del 65C02, por lo que no les hubiese costado nada igualar la velocidad de la PC-Engine, pero claro, sería un sinsentido con ROMS extremadamente lentas en los cartuchos que añadían ciclos de más al tiempo en que tardaban en ejecutarse las instrucciones.

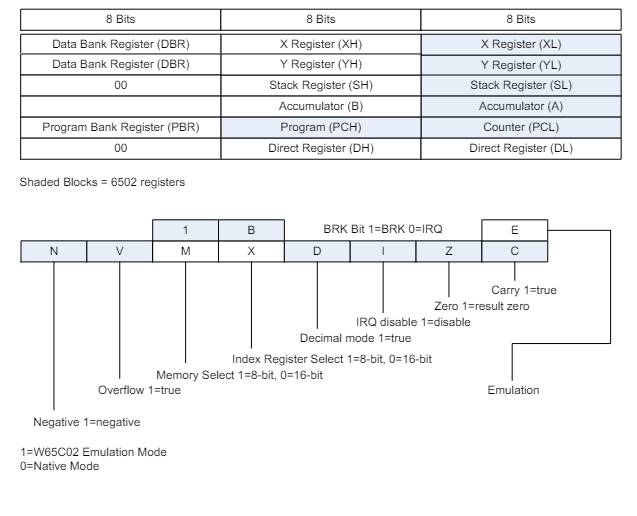

Registros del 6502 en el 65C816

El 65C816 hereda los mismos registros que el MOS 6502 y sus versiones mejoradas, pero expandiendo estos y añadiendo otros adicionales.

- El registro acumulador A sigue siendo de 8 bits; sin embargo, la ALU ahora es de 16 bits. Y es que ahora existe el nuevo registro base (B) también de 8 bits, el cual reduce la cantidad de ciclos en ciertas instrucciones aritméticas.

- Gracias a ello, las instrucciones aritméticas que funcionan con dos operandos reciben una mejora del 60% respecto al 6502.

- Los registros X e Y han pasado a ser de 16 bits, pero divididos cada uno en dos subregistros de 8 bits. XH y XL, por un lado, e YH e YL por el otro.

- En modo emulación y al igual que ocurre con el registro B, los registros XH e YH no se activan.

- Por desgracia solo hay 24 pines de direccionamiento, por lo que lo máximo que puede direccionar son 16 MB.

- El registro Data Bank Register permite seleccionar el banco de memoria.

- El Stack Pointer (SP) también es de 16 bits y dividido también en dos subregistros de 8 bits, lo bueno es que ahora esta puede ser de hasta 64 KB de tamaño.

- El contador de Programa (PC) ahora es de 24 bits, dado que está compuesto por 3 registros de 8 bits que marcan la dirección de memoria de la siguiente instrucción, el tercero es el llamado Program Bank Register (PBR).

- En cuanto el registro de estado, este se ha alargado de 8 a 16 bits, y se han añadido los siguientes flags o bits de estado:

- El flag de selección de tamaño de memoria (M) permite seleccionar si los datos son de 8 o 16 bits.

- En cambio, el flag índice (X) indica si los valores que usaran los registros X e Y son de 8 o 16 bits.

- Por último tenemos el flag E (emulación), si este se activa, el 65816 actuará de la misma manera que un 65C02 y no reconocerá ni los registros y tampoco las nuevas instrucciones.

El registro D

En modo emulación, donde el 65C816 se comporta como un 6502, la page zero se encuentra en los primeros 256 bytes de memoria y se gestiona a través del registro X, pero en modo nativo de esta CPU de 16 bits, el acceso se hace a través del registro D, el cual es de 16 bits y apunta a los primeros 64 KB de memoria, a los que este microprocesador accederá en muchos menos ciclos de reloj que el resto de la RAM del sistema, tal y como ocurre con su antecesor de 8 bits.

Esto supone un problema, por el hecho que el 65C816 no expande el set de instrucciones a 16 bits para el acceso a la Page Zero, por mucho que exista una versión ampliada del registro X. Por lo que muchos programadores que sabían desarrollar para el 6502 simple y llanamente ignoran este registro y sus instrucciones, perdiendo rendimiento en el proceso, pero es lo que tiene la retrocompatibilidad hacia atrás que un peor diseño también se hereda.

Y es que si tu programa ya te funciona con el 6502 y lo quieres pasar a 16 bits, pues usarás el código menos eficiente. Lo mismo se puede decir de las instrucciones para mover datos en bloque son nuevas en el 65C816 y que muchos programas no utilizan. En todo caso, parte de su fracaso se debe a que cuanto salió, tanto el Motorola 68K como el Intel 8086 ya se habían repartido todo el pastel de las CPU de 16 bits.

El Ricoh 5A22

Mientras que el 6502 tuvo una gran cantidad de variaciones, el 65C816 solo tuvo una, el injustamente tratado 5A22. Y es que inicialmente Nintendo tenía pensado hacer compatible hacia atrás su consola de 16 bits con la Famicom, de ahí la elección de esta CPU para la Super NES/Super Famicom.

Como ya hemos comentado antes, la mala fama le viene por una mala arquitectura que rodea a este chip. Se trata de un 65C816 con una serie de cambios realizados por Ricoh y la propia Nintendo, entre los que destacan los siguientes:

- Una unidad DMA para acceder de forma directa a la VRAM con dos modos distintos y que es análoga a la que tiene Genesis/Mega Drive

- El primero puede transmitir información durante el periodo VBlank a una velocidad de 2.68 MB/s.

- En cuanto al segundo, se utiliza en el periodo HBlank de cada línea de escaneo activa. Por lo que es conocido como HDMA.

- Aparte de los 24 pines de direccionamiento del 65C816, el 5A22 añade otros 8 adicionales, que sirven para la comunicación directa entre la CPU y ciertos registros de los chips gráficos y de sonido.

Con esto terminamos nuestro extenso artículo acerca del MOS 6502 y sus diferentes derivados. Para detalles únicos de cada uno de los diferentes sistemas os recomendamos leer los artículos correspondientes a cada uno de ellos, los cuales irán apareciendo con el tiempo en esta página