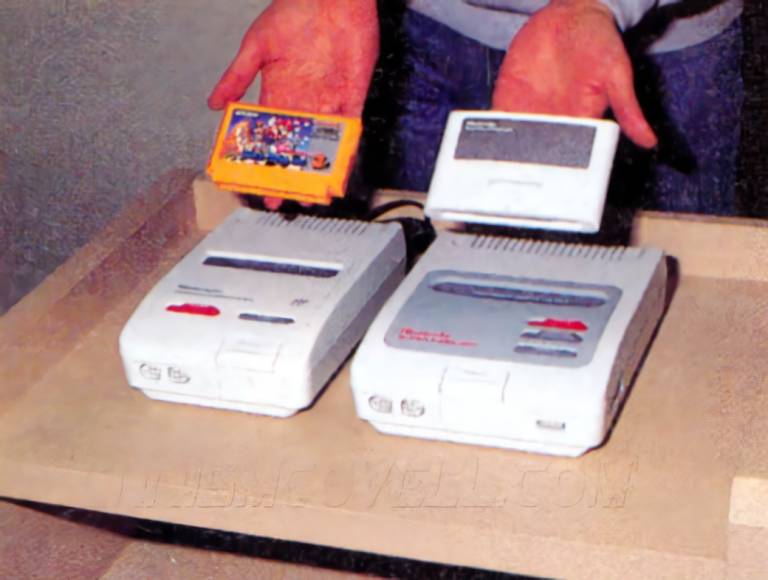

Lanzada bajo el epíteto de «Cerebro de la bestia» en el mercado español, la Super NES es la demostración de que las segundas partes no fueron siempre malas. Sin embargo, su hardware no ha estado jamás exento de polémicas por ciertas decisiones que tomó Nintendo a la hora de diseñarla. Lo que aún hoy en día toma genera líneas de tinta tanto real como virtual a la hora de compararla con sus rivales. No obstante, en este artículo nos centraremos en describir el hardware de la consola, sin hacer comparativas de ningún tipo con sus rivales.

El 5A22, la polémica CPU de Super NES

Para la CPU de Super NES, Nintendo volvió a confiar en Ricoh para el diseño y la fabricación de la misma, a la cual bautizaron como S-CPU y 5A22. De nuevo nos encontramos con una variante a medida de una CPU conocida, en este caso se trataba del 65C816 de Western Digital, una variante de 16 bits del MOS 6502 que ya habíamos visto previamente en el Apple II GS. Una elección polémica, que se dice que se dio por el hecho de que los de Kyoto inicialmente buscaron la compatibilidad hacia atrás, pero las razones son más oscuras. En todo caso, carece del generador de audio de su predecesor de 8 bits, por lo que no podría reproducir los juegos de forma directa.

La segunda mitad del 5A22 es una unidad DMA de 8 canales, 2 de los cuales pueden enviar datos durante el periodo HBlank del dibujado en pantalla. Su trabajo es el mismo que el de la unidad homónima de Mega Drive, solo que no se encuentra en el chip gráfico sino en la propia CPU. No obstante, al interconectar la CPU con más componentes, es también más complejo que en la consola de SEGA y es uno de los elementos que hacen que desarrollar para la consola de Nintendo fuera un desafío en comparación a hacerlo con otras arquitecturas de la época, especialmente para aquellos que por aquel entonces trabajaban haciendo juegos utilizando el 68000 de Motorola, ya que no solo tenían que lidiar con las limitaciones del 65C816, sino también con la unidad DMA.

Las limitaciones del 65C816

Cuando MOS Technologies diseño el 6502, con respecto a la integración, ningún chip llegaba a superar los 10.000 transistores, por lo que los conjuntos de registros e instrucciones eran limitados. Años más tarde, con la aparición del microprocesadores como el 68000 de Motorola y el 8086 de Intel, donde ya se podían crear chips con casi 100.000 transistores, los conjuntos de instrucciones se hicieron más complejos. No obstante, el 65C816 que usó Nintendo para Super NES se quedó casi con el mismo set de instrucciones incompleto del 6502, eso sí, con alguna instrucción adicional, pero carecía de muchas instrucciones básicas que sí que se encuentran en otras CPU.

El motivo de ello es que hablamos de un chip de solo 22000 transistores, lo que tiene varias consecuencias. Entre ellas estaba una falta total de ortogonalidad, que significaba que no todas las instrucciones tenían su variante para los diferentes modos de direccionamiento. Lo que hacía que fuera un infierno para los compiladores. Mientras que con el 68000 los desarrolladores podían programar en lenguajes como C, aunque eso los hacía dependientes del compilador, en el 65C816 no quedaba otra que programar a mano en ensamblador y con un código, por la falta de instrucciones, menos amigable para los desarrolladores.

Se dice que es una CPU RISC, nada más lejos de la realidad. Era un diseño extremadamente simple cuando se lanzó por primera vez en 1984 para el Apple II GS y lo fue aún más para una consola de 1990, pero para Nintendo era barato y les daba control sobre la exclusividad de los videojuegos para su plataforma, lo que tuvo una serie de consecuencias a nivel técnico y político para la empresa liderada por Hiroshi Yamauchi.

Modos mixtos y direccionamiento incómodo

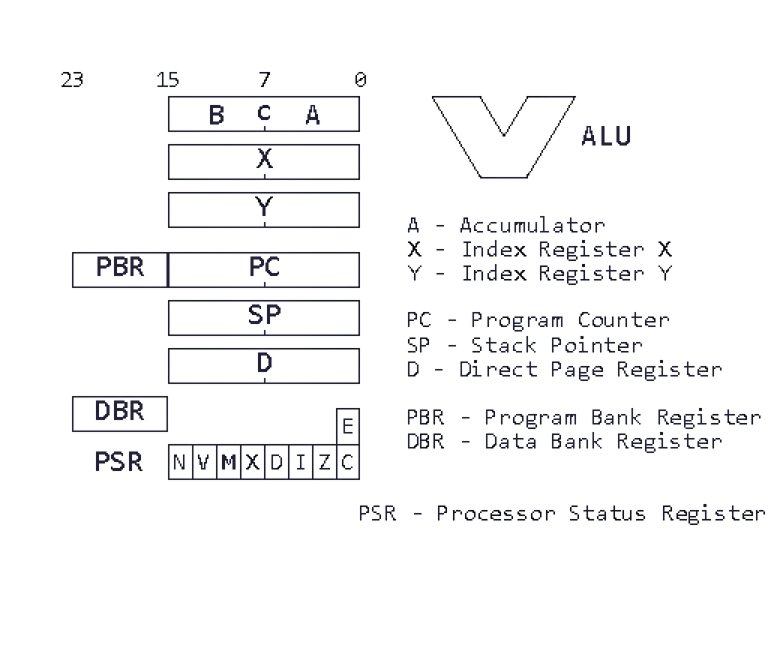

Uno de los mayores problemas del diseño del 65C816 es que puede funcionar en 2 modos distintos: 8 y 16 bits. Es por ello que introduce 2 bits adicionales en los bits de estado en el Processor Status Register, el cual es el registro donde se almacenan los bits de estado o FLAGS. El motivo de ello es que, dependiendo del modo en el que se encuentre la CPU, se interpretará el código binario de una forma u otra dada la longitud de las instrucciones. Es por ello que se modifican dos instrucciones:

- El cuarto bit indica el tamaño de los registros índice (X) e (Y).

- El quinto bit del registro determina el tamaño del registro acumulador (A) y las operaciones de memoria relacionadas.

Para hacerlo, se invocan las instrucciones SEP que pondrá a la CPU en modo de 8 bits al activar ambos bits y REP a modo de 16 bits al desactivarlos. Es por ello que el 65C816 no es directamente retrocompatible con el software del 6502, a no ser que se le envíe la señal a esos dos pines de forma externa que lo coloque en modo 8 bits. Además, en modo 16 bits, la ventaja es que puede dividir el registro acumulador en 2 registros de 8 bits para realizar operaciones aritméticas de dos operandos, reduciendo los accesos a memoria. Aunque parezca sorprendente, Muchos desarrolladores estaban familiarizados con el 6502 y esto facilitaba la transición del código.

Acceso a memoria en el 65C816

El 65C816 nació como una evolución natural del 6502, pero su diseño terminó siendo una mezcla incoherente de compromisos que entorpecen tanto la programación, la implementación en el hardware y también su rendimiento. Hemos de partir del hecho de que el chip original lo diseñó Western Digital para el Apple II GS y que se vio limitado al tener que usar un encapsulado de 40 pines.

Una de las particularidades del 65C816 de Super NES es que su contador de programa es de 16 bits, su registro de pila es también del mismo tamaño, pero su direccionamiento es de 24 bits. Ahora bien, no dispone de esa cantidad de pines, sino solo de 16. La trampa está en que trabaja con 256 bancos de 64 KB cada uno. A la hora de acceder a memoria, la selección de banco es realizada a través de los pines de datos que se encuentran multiplexados para ese propósito, lo que se traduce en que si un programa requiere múltiples bancos, hay que añadir un ciclo de instrucción adicional para el acceso a memoria.

La otra limitación es el bus, el cual es solo de 8 bits, lo que añade otro ciclo para la instrucción. Sin embargo, Nintendo resolvió esta limitación en Super NES a través de la inclusión de una unidad DMA integrada en el 5A22 junto a la CPU y que funciona en paralelo al microprocesador. Su trabajo es gestionar los accesos a memoria no solo del 65C816, sino de todos los componentes de la consola a la memoria RAM y la comunicación entre estos. La ventaja de dicha unidad es que puede realizar una instrucción a memoria en un solo ciclo a 2.68 o 3.58 MHz dependiendo de la velocidad de la memoria a la que tengan que acceder.

La unidad DMA de Super NES

Como ya hemos visto, la CPU de Super NES era más lenta por ciclo de reloj que el 6502 de NES por el hecho de que requiere más ciclos de reloj para acceder a memoria. Si bien el 65C816 disponía de una instrucción para mover bloques de datos de una parte de la memoria a otra. La realidad es que para las necesidades de una consola de videojuegos era muy lenta. Durante el diseño de la consola, los ingenieros de Nintendo bajo el mando de Uemura se dieron cuenta de las limitaciones del 65C816, pero no querían perder la capacidad de poder reusar el código de y las herramientas que habían desarrollado alrededor del 6502, por lo que la solución fue una unidad DMA, la cual se encargase de realizar las operaciones de lectura y escritura de la CPU con la memoria, los periféricos y otros componentes.

Por lo que no deja de ser el medio principal para actualizar gráficos, paletas, y efectos visuales o de sonido sin intervención activa del CPU y en menos ciclos de lo que necesitaría esta. No obstante, la unidad DMA de Super NES es algo más compleja que la de Mega Drive, ya que soportaba 8 canales DMA en total. Esto no se traduce solo en 8 caminos distintos dentro de la circuitería, sino que puede manejar hasta 8 procesos de accesos simples a memoria o para copiar bloques de datos de un componente de la consola a otro.

La única diferencia es que los canales de número más bajo tienen más prioridad a la hora de ejecutarse y que el mecanismo funciona en ráfagas y no concatenado con la CPU, por lo que no le dará poder a la CPU hasta que no haya ejecutado el traspaso de datos, tiempo en que el propio 65C816 estará parado.

Unidad HDMA

Al igual que Game Boy, Super NES incluye una unidad HDMA, la cual se activa a partir del sexto píxel en el periodo HBlank, lo cual da algo de tiempo para cambiar al vuelo ciertos registros, especialmente de las S-PPU para conseguir efectos gráficos avanzados. Ambas unidades tienen acceso a los 8 canales DMA, pero la diferencia es que la unidad HDMA solo está activa en dicho periodo, puede enviar pocos bytes, no más de 16 por línea y tiene preferencia a la unidad DMA.

La utilidad del HDMA no puede parecer clara al principio, pero especialmente tiene la capacidad de poder modificar los registros de ambas S-PPU en la consola para poder cambiar la forma de generar los gráficos de una pantalla a otra. En realidad, no deja de ser lo mismo que las listas de pantalla del ANTIC de la Atari 800, y sí, Nintendo en este caso volvio a copiar una función de dicho ordenador en sus consolas de videojuegos.

Mapa de memoria y velocidad de acceso

Una de las particularidades del 65C816 respecto al 6502 es el hecho de disponer de un bus de direcciones de 24 bits, sin embargo, al contrario que el 68000 que opera con registros de 32 bits y le permite llenar una petición al bus en un solo ciclo en este caso nos encontramos con que los registros son de 16 bits para la dirección de memoria y de 8 bits para la selección de banco. Si la CPU accede al banco de memoria actual, entonces el proceso se realiza en un solo ciclo de reloj. No obstante, si se ha de cambiar de banco, entonces hay que añadirle un ciclo de reloj de acceso adicional. Se ha de decir que el microprocesador de Super NES en ningún momento utiliza direccionamiento absoluto, sino banco + dirección dentro del mismo para acceder a la información.

| Banco(s) | Dirección (hex) | Tamaño (bytes) | Velocidad | Descripción |

|---|---|---|---|---|

| 0–63 | $0000–$1FFF | 8192 | 2.68 MHz | RAM principal (WRAM) |

| $2000–$20FF | 256 | 3.58 MHz | Área general de E/S o mapeo especial | |

| $2100–$21FF | 256 | 3.58 MHz | S-PPU | |

| $2200–$3FFF | 7680 | 3.58 MHz | Área general de E/S o mapeo especial | |

| $4000–$41FF | 512 | 1.79 MHz | Registros internos de la CPU | |

| $4200–$43FF | 512 | 3.58 MHz | Registros internos de la CPU | |

| $4400–$5FFF | 7168 | 3.58 MHz | Área general de E/S o mapeo especial | |

| $6000–$7FFF | 8192 | 2.68 MHz | Área general de E/S o mapeo especial | |

| $8000–$FFFF | 32768 | 2.68 MHz | ROM del cartucho o expansión | |

| 64–125 | $0000–$FFFF | 65536 | 2.68 MHz | ROM del cartucho o expansión |

| 126–127 | $0000–$FFFF | 65536 | 2.68 MHz | RAM principal (WRAM) |

| 128–191 | $0000–$1FFF | 8192 | 2.68 MHz | RAM principal (WRAM) |

| $2000–$20FF | 256 | 3.58 MHz | Área general de E/S o mapeo especial | |

| $2100–$21FF | 256 | 3.58 MHz | S-PPU | |

| $2200–$3FFF | 7680 | 3.58 MHz | Área general de E/S o mapeo especial | |

| $4000–$41FF | 512 | 1.79 MHz | Registros internos de la CPU | |

| $4200–$43FF | 512 | 3.58 MHz | Registros internos de la CPU | |

| $4400–$5FFF | 7168 | 3.58 MHz | Área general de E/S o mapeo especial | |

| $6000–$7FFF | 8192 | 2.68 MHz | Área general de E/S o mapeo especial | |

| $8000–$FFFF | 32768 | Variable | ROM del cartucho o expansión | |

| 192–255 | $0000–$FFFF | 65536 | Variable | ROM del cartucho o expansión |

La realidad es que la velocidad de reloj del 5A22 se consigue dividiendo el reloj maestro del sistema (21.48 MHz) entre 6 para los accesos rápidos (3.58 MHz) y 12 para los muy lentos (1.79 MHz), dado que ambas señales están sincronizadas se utilizan para los accesos a los registros internos o para acceder a áreas fuera de la RAM principal. Sin embargo, para acceder a la RAM del sistema y al cartucho, la división es por 8 (2.68 MHz), lo que corresponde a los accesos lentos. Si bien lo ideal sería que la mayoría de operaciones se hicieran en los registros internos, hemos de recordar que estamos hablando de una CPU que tiene un solo registro acumulador, lo cual fuerza a que la mayoría de veces las operaciones se realicen sobre la memoria principal.

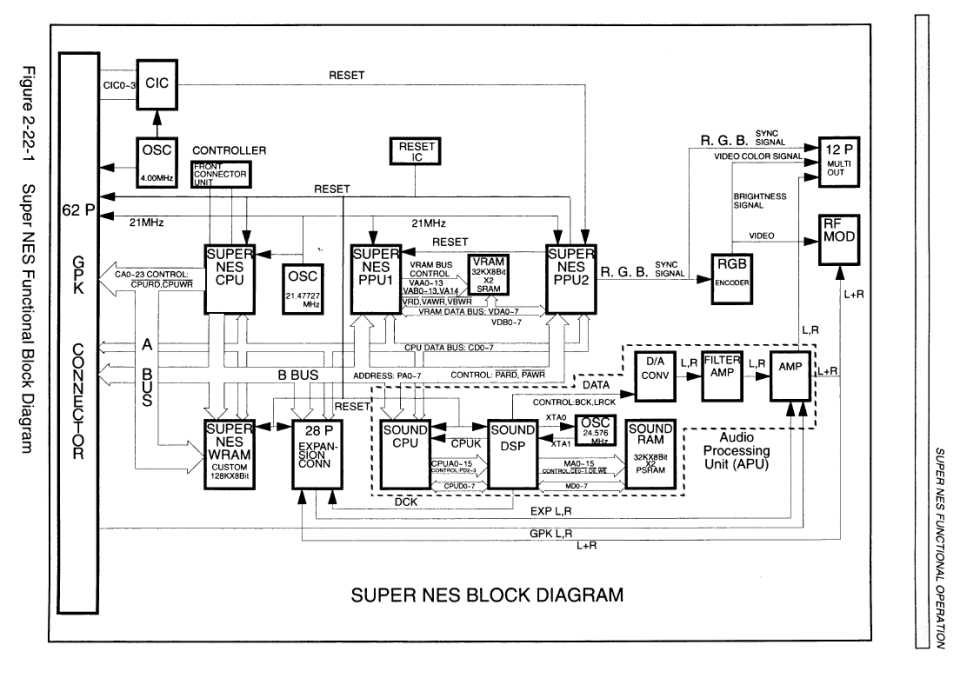

Bus A y Bus B

Super NES contaba con dos buses de direccionamiento: uno de 24 bits, denominado Bus de Direccionamiento A, y otro de 8 bits, conocido como Bus de Direccionamiento B. La forma en que los distintos dispositivos de la consola estaban conectados a ambos buses se puede ver en el siguiente diagrama donde se puede ver la organización interna de los diferentes elementos de la consola.

El bus A es el que se encuentra mapeado al bus de direcciones del 5A22/65816, por lo que puede direccionar hasta 16 MB de memoria en total. A través de dicha vía de comunicación, la consola tiene acceso a los 128 KB de memoria RAM del sistema, llamada WRAM y al contenido de los cartuchos. Mientras que al Bus B se encuentran conectados ambas Super PPU y el DSP de audio creado por Sony para Nintendo, el SPC700. Este se utiliza para configurar en cada frame ambos chips de apoyo, ya que solo direcciona 256 bytes en total situados en el banco actual.

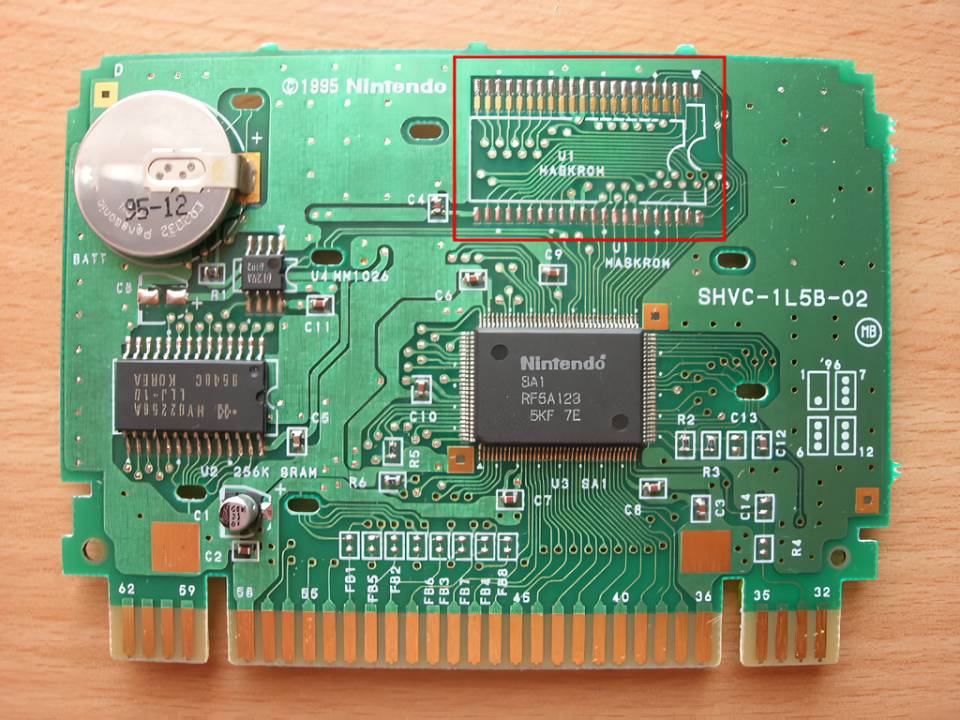

El SA-1

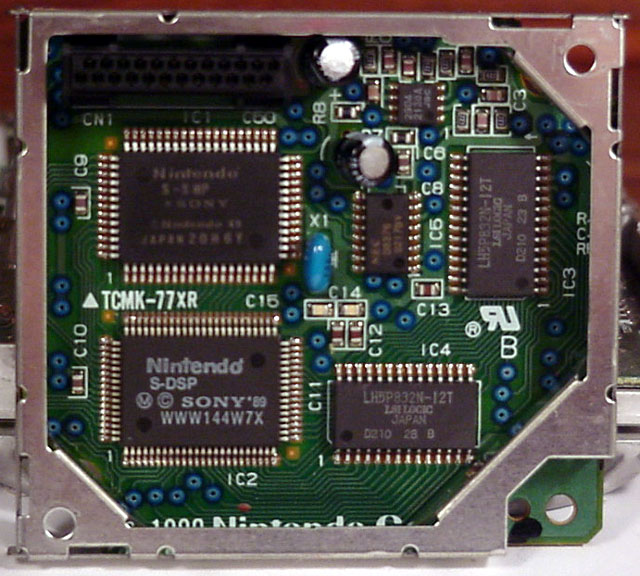

Debido a las limitaciones de la CPU de Super NES, Nintendo añadió en los cartuchos hardware adicional para mejorar las capacidades de la consola más allá del hardware base. Lo que en muchos casos encarecía el coste de los videojuegos. Los dos casos más conocidos son el SA-1, el cual era un 5A22 pero funcionando a 10.74 MHz y ambos chips SuperFX.

En el caso concreto del SA-1, pese a su mayor velocidad de reloj, carece de las unidades DMA/HDMA de la CPU de Super NES, la cual usa como coprocesador para comunicarse con la memoria del sistema, aunque dispone de su propia RAM. Además, el SA-1 integra una unidad que sirve para convertir búferes de imagen enteros en formatos de patrones/sprites y paletas que las S-PPU pueden manejar y entender. Esto resulta muy útil a la hora de portar juegos desde otras plataformas que basaban ya sus gráficos en un búfer de imagen y no en el uso de patrones/sprites.

Gráficos en la Super NES

El subsistema gráfico de Super NES se vio influenciado por el de PC-Engine, ya que al igual que este, es una evolución del de Famicom/NES y también se encuentra compuesto por dos chips distintos, llamados S-PPU 1 y S-PPU 2, cuyas funciones son las mismas que el HuC6270 y HuC6260 de la consola de NEC respectivamente. No obstante, la potencia gráfica de Super NES es muy superior a la consola diseñada por Hudson Soft, ya que no solo soporta una mayor cantidad de modos gráficos que sus rivales, sino también con mayores especificaciones.

| Modo | Sprites | Tilemap 0 | Tilemap 1 | Tilemap 2 | Tilemap 3 |

|---|---|---|---|---|---|

| 0 (256 x 224) | 16 colores | 4 colores | 4 colores | 4 colores | 4 colores |

| 1 (256 x 224) | 16 colores | 16 colores | 16 colores | 4 colores | No disponible |

| 2 (256 x 224) | 16 colores | 16 colores | 16 colores | No disponible | No disponible |

| 3 (256 x 224) | 16 colores | 256 colores | 16 colores | No disponible | No disponible |

| 4 (256 x 224) | 16 colores | 256 colores | 4 colores | No disponible | No disponible |

| 5 (512 x 224) | 16 colores | 16 colores | 4 colores | No disponible | No disponible |

| 6 (512 x 224) | 16 colores | 16 colores | No disponible | No disponible | No disponible |

| 7 (256 x 224)) | 16 colores | 256 colores | No disponible | No disponible | No disponible |

El problema es que la mayoría de los juegos no usaron la mayoría de los modos gráficos que otorgaba el subsistema gráfico de Super NES, lo que se traduce en que Nintendo complicó las cosas más de lo normal a la hora de diseñar estos chips, especialmente el S-PPU 1. Tened en cuenta que estos diseños son microcableados, no son como las GPU de hoy en día que ejecutan programas, por lo que el funcionamiento de cada uno de los modos gráficos se implementó dentro del hardware, consumiendo transistores, es decir, espacio en el chip. Tenemos casos como el Modo 1 y el Modo 7 que se utilizaron ampliamente en los juegos, pero el resto de modos fueron en gran parte ignorados por completos o utilizados de forma muy esporádica. Esto provocó que la mayoría de la lógica cableada del chip terminara sin utilizarse.

El modo 7 y el DSP-1

De los 7 modos gráficos de Super NES, el más icónico es el llamado Modo 7, que permite que un fondo pueda ser rotado, escalado o sesgado. No obstante, el 5A22 no tiene la suficiente potencia para mover los gráficos en dicho modo a la suficiente velocidad. Por lo que Nintendo incluía en los cartuchos de los juegos que usaban ese modo un chip de apoyo adicional, el DSP-1. El motivo de ello es que el set de instrucciones de la CPU no soportaba ciertas funciones matemáticas que eran esenciales para hacer funcionar dicho modo.

Al contrario que otros chips de apoyo, el DSP-1 no reemplaza al 5A22, sino que funciona como coprocesador de este. Simplemente, la CPU de Super NES le envía la instrucción y el dato al DSP-1 y este lo calcula y vuelve el resultado de vuelta. En cuanto al tipo de instrucciones que soporta, hablamos de operaciones trigonométricas a gran velocidad. Las cuales realiza en muy pocos ciclos de reloj.

Sprites

La Super NES fue el último sistema que salió al mercado que fue una evolución del diseño del TMS9918A y podríamos considerarlo el más potente de todos si no fuera por la existencia del X68000. Ahora bien, al igual que el ordenador de Sharp puede colocar hasta 128 sprites distintos en pantalla, y el doble de ellos por línea de escaneo. Claro está que la trampa es que la consola de Nintendo opera con sprites de 8 x 8 píxeles en vez de 16 x 16 píxeles. Sin embargo, hemos de tener en cuenta que el límite de sprites que puede mostrar está directamente relacionado con la resolución horizontal que ocupan, como en cualquier sistema no se pueden mostrar más que el límite que permite la resolución de pantalla.

Al igual que la NES/Famicom, la Game Boy y la PC-Engine de NEC, volvemos a tener de nuevo la tabla de atributos de los sprites dentro de la memoria interna, esta vez del S-PPU 1, lo que le permite acceder a ella en un solo ciclo, en vez de los 2 que se necesitarían si esta se encontrase en la memoria externa. En este caso, la tabla de atributos es de 4 bytes por sprites, por lo que ocupa 512 bytes de manera interna y su configuración es la siguiente:

| Byte | Bits | Descripción |

|---|---|---|

| 0 | 0-7 | Posición horizontal, en los modos de 512 pixeles en horizontal, cada unidad representa 2 píxeles |

| 1 | 0-7 | Posición vertical. si se usa el modo progresivo (448 líneas a 30 FPS) entonces cada valor son 2 líneas |

| 2 | 0 | El sprite se dibuja verticalmente invertido |

| 1 | El sprite se dibuja horizontalmente invertido | |

| 2-3 | Prioridad del sprite respecto a los fondos:

|

|

| 4-6 | Selección de paleta (8 paletas posibles de 16 colores cada una) | |

| 7 | Indice de sprites | |

| 3 | 0-7 |

Además, la S-PPU 1 tiene una segunda OAM de solo 32 bytes, la cual almacena información del tamaño de cada sprite, soportando Super NES tamaños que van desde los 8 x 8 a los 64 x 64 píxeles por sprite. Ahora bien, los patrones son de 8 x8 píxeles, por lo que son más grandes. Al igual que en otros sistemas de 16 bits, los sprites más grandes construían juntando varios patrones en un mismo sprite.

Tilemaps

La cantidad de tilemaps o fondos en pantalla dependía del modo gráfico utilizado y de que toda la información gráfica cupiese en la VRAM, la cual era solo de 64 KB, la misma cifra que PC-Engine y Mega Drive. Al igual que ocurre con el resto de sistemas, y a diferencia de los sprites que se actualizan en cada fotograma, el mapa de caracteres solo se carga desde el cartucho a la VRAM en los saltos de un nivel a otro desde el cartucho a la memoria de vídeo. Dado que la resolución estándar de Super NES es de 256 x 224, esto significa que maneja 32 x 28 caracteres por tilemap, pero aquí hemos de tener en cuenta que hablamos de hasta 3 fondos distintos y cada carácter en el mapa requiere 2 bytes de información, organizados de la siguiente manera:

| Byte | Bit | Función |

|---|---|---|

| 0 | 0 | Verticalmente el Patrón/Sprite se dibuja a la inversa. |

| 1 | Horizontalmente el Patrón/Sprite se dibuja a la inversa. | |

| 2 | Prioridad (permite colocar el fondo por delante de los sprites si se activa) | |

| 3-5 | Selección de paleta | |

| 6 | En los modos 3 y 7 se usa como 1 bit de paleta adicional, permitiendo llegar a los 256 colores. | |

| 7 | Selección de banco en la VRAM | |

| 1 | 0-7 | Indice del patrón en el banco de VRAM. |

Al contrario que la NES/Famicom, Super NES no hace separación entre datos y gráficos en el cartucho, sino que están unificados en la ROM, por lo que se vuelcan al cartucho al principio de cada nivel, ya que la consola no es lo suficientemente rápida como para ir actualizando cada uno de los caracteres de los diferentes tilemaps al vuelo.

Color

Pese a que la función de la S-PPU 2 es la misma que el HuC6260, es decir, gestionar el color de la escena, hemos de partir del hecho de que en Super NES tenemos un DAC RGB de 15 bits que le da un rango de 32.768 colores distintos. No obstante, utiliza la estrategia de tener una Color RAM interna de Mega Drive y Mark III/Master System. En este caso tenemos 2 2 bancos de 256 bytes cada uno. En cada banco puede almacenar hasta 8 paletas distintas de 16 colores cada una (15+transparente), haciendo el total de 256 colores en pantalla que puede reproducir la consola.

No obstante, una de las cosas a destacar de Super NES es que hereda de otros sistemas la capacidad de realizar operaciones lógicas entre dos patrones situados en una misma posición, combinando su valores para realizar efectos especiales como las simulaciones de transparencias en algunos casos. La forma de conseguirla es similar a la utilizada en los Blitter o en sistemas como el PC-98, realizando operaciones lógicas con dos fuentes y un destino. La única diferencia es que ambas S-PPU no tienen la capacidad de mover memoria de un lado a otro. Otro de los puntos fuertes es la posibilidad de cambiar dinámicamente y al vuelo los colores de una línea de escaneo usando el HDMA para modificar la la Color RAM interna. Lo que permite efectos de degradados de color, por ejemplo.

SuperFX

El SuperFX fue un coprocesador creado por Argonaut para Nintendo, famoso por haber sido empleado en varios juegos de Super NES para ir más allá de los límites de la consola. Títulos como Star Fox, Yoshi’s Island usan este chip, también juegos como la conversión de Doom, pero esta es mejor olvidarla por su reducida resolución, falta de contenido e ir a 15 FPS, aún así fue un hito teniendo en cuenta la potencia de la consola y su arquitectura.

Al contrario de lo que muchos piensan, no se trataba de una CPU que reemplazará a la original y debemos verlo más bien como un DSP-1 glorificado, pero 4 u 8 veces (10.74 MHz o 21.48 MHz) más rápido en velocidad de reloj al disponer de su propia memoria RAM y tener su propio caché, aunque solo de 512 bytes. Además de que puede realizar muchas de sus instrucciones en un solo ciclo de reloj.

Ahora bien, su mayor capacidad es la de poder crear un búfer de imagen tradicional que luego copia en la VRAM de ambas S-PPU. El SuperFX está diseñado para convertir el búfer de imagen generado en un Tilemap compuesto por bloques de 8×8 píxeles. Eso sí, el límite es tanto la RAM del cartucho como la propia VRAM de Super NES, la cual limita la resolución de salida, la cual, como mucho, puede ser de 256 x 192 píxeles.

Audio en la Super NES

Sin duda, el componente más famoso de la consola de 16 bits de Nintendo es el SPC700, el DSP creado por Sony para la consola con la capacidad de reproducir hasta 8 pistas PCM de forma simultánea y que le dio la superioridad sonora a la Super NES respecto a sus rivales. Se trata de un sistema de audio diseñado por Ken Kutaragi, quien años más tarde sería el diseñador jefe de la primera PlayStation.

El contrario de otros sistemas de audio como el Paula del Commodore Amiga, el SCP700 no accede a la RAM principal del sistema y tampoco a la memoria del cartucho, por lo que se encuentra limitado a los 64 KB de memoria que tiene asignados para él mismo. Esto significa que la CPU de la consola ha de enviar la lista de comandos, así como los samples de audio a la Sound RAM, a la que acceden tanto el S-SMP como el S-DSP, que son los chips principales que componen el SPC700. Ambos chips en revisiones más tardías de la consola se unificaron en uno solo.

| Característica | Detalle |

|---|---|

| Canales PCM | 8 |

| Resolución de audio | 16 bits por muestra |

| Compresión de muestras | BRR (Bit Rate Reduction), una variante de ADPCM |

| Frecuencia de muestreo máxima | Hasta 32 KHz por canal |

| Control estéreo | Control de volumen independiente para canal izquierdo y derecho. |

| Envolventes | Soporte para ADSR (Attack, Decay, Sustain, Release) |

| Efectos DSP | Eco/reverberación, modulación de tono (pitch modulation) |

| Tiempo de mezcla interna | Mezcla de los 8 canales en 32 kHz |

El trabajo del S-SMP (un 6502 modificado) es el mismo que el del Z80 en la Mega Drive, controlar la generación del audio y liberar a la CPU para ello. Por lo que es el que interpreta los comandos enviados por el 5A22 y se encarga de manejar al S-DSP para generar el sonido. Por lo que fuera de la carga de nuevos datos al principio de cada nivel, el SPC700 funciona de manera aislada al resto del sistema.

Las motivaciones de Nintendo

Cuando Super NES estuvo en desarrollo, los medios japoneses de la época hablaban de que la sucesora de la NES/Famicom sería compatible hacia atrás, algo que para muchos explica la elección del 65C816 como CPU de la Super NES. No obstante, eso es un mito, ya que desde la primera presentación de la consola, realizada en 1988, Nintendo ya confirmó a los medios que la consola de 16 bits no sería compatible hacia atrás.

La elección se hizo para dificultar la conversión de títulos de Super NES a las plataformas de la competencia. En Japón, el 65C816 era un chip muy poco conocido, al igual que su antecesor. Solo los desarrolladores que habían trabajado en la consola de 8 bits de Nintendo conocían cómo trabajar con él. Por lo que las empresas tenían departamentos enteros que estaban enfocados en realizar juegos para Famicom y otros para el resto de sistemas. Esto le dio a Nintendo un aura de exclusividad en el catálogo, ya que el portar juegos se hizo relativamente complicado. En todo caso, esto tenía un arma de doble filo en forma de conversiones de recreativa mal programadas, como es el caso del Joe and Mac de Data East o el Gradius III de Konami.

Y la táctica les funcionó, la popularidad de Famicom movió al público a Super Famicom y con ello la mayoría de las pequeñas editoras y estudios de desarrollo se movieron con sus clientes. Por si fuera poco, Super NES vendía bien en todo el mundo. Mientras que PC-Engine solo lo hacía bien en Japón y Mega Drive vendía mal en el país del sol naciente.